Contact scaling is a major challenge in nano complementary metal–oxide–semiconductor (CMOS) technology, as the surface roughness, contact size, film thicknesses, and undoped substrate become more problematic as the technology shrinks to the nanometer range. These factors increase the contact resistance and the nonlinearity of the current–voltage characteristics, which could limit the benefits of the further downsizing of CMOS devices.

1. Introduction

Contacts, referring to a metal’s connection to a semiconductor or insulating film, are integral parts of all electronic devices. To exploit the electronic properties of electronic devices to a large degree, it is essential to produce ohmic contacts that allow for efficient and nondistorted signal transmission. Over decades of significant effort, solid theoretical accomplishments related to metal/semiconductor interfaces, and Schottky junction charge transport studies, as well as developments in the technological know-how for achieving good ohmic contacts, during the period from the 1930s to 1950s, contacts for microelectronic devices were not considered a major challenging issue. In the last couple of decades, contacts reappeared as a challenging issue with the aggressive downsizing of complementary metal–oxide–semiconductor (CMOS) devices and the introduction of 2D materials, such as graphene, carbon nanotubes, and 2D transition metal dichalcogenides.

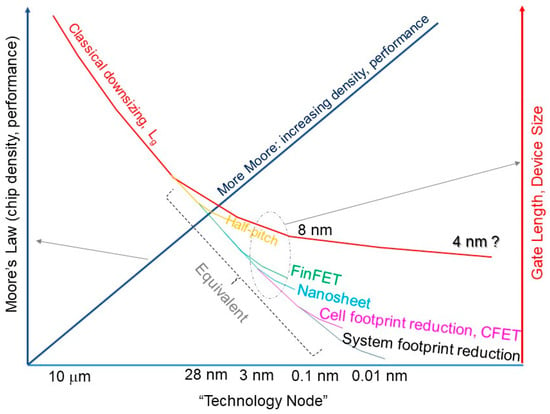

In the era of metal–oxide–semiconductor (MOS) or complementary MOS (CMOS) technology, many efforts have been devoted to the technology and the structural advancement of devices for the continual downsizing of the gate length and increasing of the integration density

[1][2][3][4][5]. As the feature size of CMOS technology approaches a few nanometers, which is considered to be the physical and technological limits, shortening of the gate length has faced ever-tougher challenges and the pace of downsizing has slowed down in recent years (see

Figure 1). The scaling rule and technology node assignment have shifted from physical gate length to equivalent gate length

[6][7][8]. For instance, for the 130 nm technology node, the physical gate length is 65 nm, and the half-pitch width is 150 nm, implying that the widths of the spacer and the source–drain regions are approximately 85 nm. For technology beyond the 45 nm technology node, the gate length is 38 nm, and the half-pitch width is 68 nm

[5], indicating a more aggressive scaling of the contact and spacer regions in later technology nodes. The source–drain contact regions have been narrowed to reduce the half-pitch size of the MOS transistor even when the gate length is not scaled according to Moore’s Law. With the FinFET technology introduced for the 28 nm technology node, the technology node assignment was based on the density level rather than the physical gate length. The 3D structure of FinFET and the larger effective gate width with a small footprint enables a higher chip density

[8][9][10]. More nonclassical or non-Denard strategies

[4], such as GAA/nanosheets, CFET, contact size reduction, cell size reduction, back power rail, buried power rail, back interconnection, nano TSV, and stacking or heterogeneous 3D packaging

[11] (see

Figure 1), will eventually be adopted to extend Moore’s Law to the subnanometer range.

Figure 1. Illustration of more Moore strategies for downsizing effective technology nodes beyond the decananometer and subnanometer ranges.

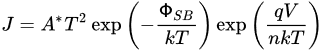

2. Schottky Junction

Long before the invention of the transistor, rectifying contacts were discovered and became a research hot spot

[12]. It is known that the contact between a metal and a semiconductor has different resistance values depending on the polarity. This property led to the development of crystal rectifiers, such as copper–cuprous oxide rectifiers, which were widely used in early AM radio receivers for signal detection. Various theories have been proposed to model the rectifying characteristics. In particular, works by Nordheim

[13], Frenkel

[14], Fowler

[15], Schottky

[16], and Mott

[17] have established a solid foundation for modern semiconductor physics, especially for current conduction across metal–semiconductor and metal–tunnel-oxide–semiconductor contacts. Schottky and Mott state that the first principle of band alignment and, thus, the barrier height is when two different materials are brought into contact. The rectifying contact resulting from a metal/semiconductor connection was later named a Schottky junction for the significant contribution of this widely accepted model.

2.1. Schottky Equation

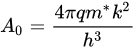

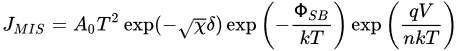

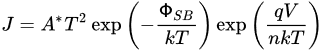

The key component of the Schottky equation is the thermal emission law, as proposed by Richardson

[18], which was based on experimental results related to the current density generated from a heated metal wire. The temperature and current dependencies are as follows:

where

W is the workfunction of the metal,

kT is the thermal voltage, and

A* is the effective Richardson constant. Schottky later modified the expression to include the effect of an electric field, and its final form is now usually expressed in terms of an applied voltage,

V, as follows

[16][17]:

where q is the electron charge, and ΦSB is the Schottky barrier.

In the original proposal by Schottky and Mott

[16][17], the Schottky barrier is as follows”

Equation (3) provides the energy difference between the metal workfunction,

ΦM, and the semiconductor affinity,

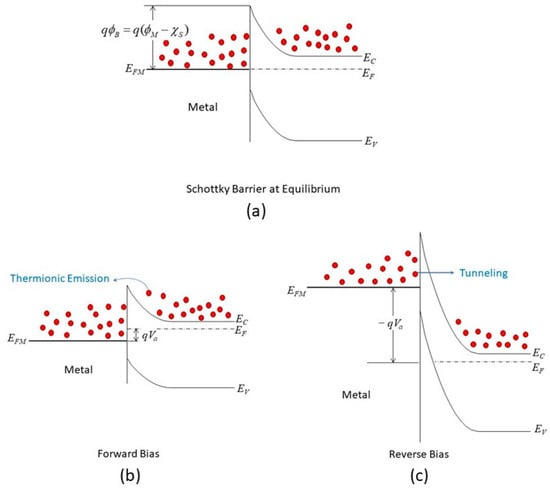

χS. The relationship is known as the Schottky–Mott rule, which describes the alignment of the energy bands when the two different materials have isolated state energies. For the case depicted in

Figure 2, an n-type semiconductor with an electron affinity smaller than the metal workfunction, equilibrium is achieved by transferring the electron on the semiconductor’s surface to the metal, as the metal workfunction is larger than the electron affinity of the semiconductor. The amount of band bending on the semiconductor’s surface is the same as the energy difference. However, the Schottky–Mott rule is not always accurate in predicting the barrier height. The Fermi level of the system tends to be pinned to a fixed position within the semiconductor bandgap, regardless of the metal used. This is because the charge distribution at the metal/semiconductor interface is not simply the sum of the charges on the isolated surfaces. There is also physical bonding or orbital overlap between the metal and semiconductor atoms, which changes the surface energy levels from their original values. This phenomenon is called Fermi-level pinning

[19][20][21]. Equation (4) approximates the Schottky barrier height with the FLP effect.

ΦSB = (S × ΦM − χS) + (1 − S)ΦMIGS (4)

where ΦMIGS is the metal-induced gap states (MIGS). The intrinsic surface states and interface dipole of the semiconductor should lead to the same consequence. The parameter S is the pinning factor, which reflects the strength of the pinning and can be determined by the slope of the barrier height versus metal workfunction plot, expressed as follows

Figure 2. Metal/n-type semiconductor Schottky contact: (a) equilibrium; (b) forward bias; (c) reverse bias.

The effective Richardson constant was later treated as a universal constant or the fundamental Richardson constant, A0, which can be calculated by finding the ensemble of electrons leaving the metal surface at a kinetic energy exceeding the Fermi level of the metal, where the energy distribution of the electrons in the metal follows the Fermi–Dirac distribution. The fundamental Richardson constant is constituted by fundamental parameters, as follows:

(6)

The fundamental Richardson constant,

A0, equals 120 A/cm

2/K

2 when the effective mass is equal to the fundamental value of the electron mass. However, the effective Richardson constant,

A*, extracted from the experimental results using (2), always differs from the fundamental value,

A0. In the Schottky diode, the thermionic emission from the semiconductor, the Richardson constant, is further modified to account for the effective mass of different bands and band structures of various materials

[22]. However, experimental results over the last 120 years have not shown that

A* is a universal constant, even when taking the effective mass into consideration for the case of thermionic emissions from semiconductors. Instead, it is often treated as an empirical parameter or a fiction of

A0 in many cases. Yet it is sound to consider the constant of a material-dependent parameter because of the different carrier velocities or lifetimes resulting from different or same materials prepared under varying conditions.

The second issue in applying the Schottky equation is that there is a vast list of publications, including numerous reports on 2D materials based on Schottky diodes or MIS Schottky diodes, that characterize the Schottky current with the “ideality factor”,

n. Taking the ideality factor into consideration, the Schottky equation becomes

[23], as follows:

(7)

The ideality factor was first defined in a pn junction diode, which has a solid physical ground, whereby if the forward current is contributed by the diffusion current only,

n = 1, and when carrier generation and recombination (GR) take place,

n = 2

[23];

n can increase up to 4 if the generation–recombination involves multiple energy levels of defects

[24][25]. Thus,

n = 1 represents an ideal diode, and

n > 1 indicates the contribution of a GR current. The ideality factor indicates the quality of the pn junction diode. In a Schottky diode, although the introduction of

n can help to improve the fitting of the voltage dependence in some cases, it is not an indicator of junction quality. It does not have a sound physical or technical meaning in many cases. The

n factor in the Schottky diode equation should be a reflection of the effectiveness of the barrier surface potential varying with the applied voltage.

2.2. Current Conduction in an MIS Diode

The Schottky equation can be used to model the current conduction of an MIS diode. However, this equation is based on some assumptions that are often overlooked. It is also suggested that, in some early metal/semiconductor contacts, there may exist some native thin oxide on the semiconductor’s surface. Fowler suggested that there was a layer of “bad semiconductor” between a metal and a good semiconductor

[15]. Although these proposals were later refuted, it did point to the importance of the interface’s quality in the contact behavior. A similar situation arose in the recent study of 2D material contacts and 2D material/Si contacts, in which a thin tunneling layer may be present between the metal and the 2D material. In this case, the Schottky equation can still be used to approximate the tunneling current in the forward region but with a modified effective Richardson constant that accounts for the tunneling barrier

[26]. The modified Schottky equation is as follows:

(8)

where is the χ mean barrier height value between the insulator and the semiconductor and δ is the tunneling oxide thickness. It can define a new effective Richardson constant as follows:

(9)

Note that the current conduction is, in fact, dominated by the direct tunneling of the carriers over the thin insulating layer. The approximation of the Schottky equation involves modifying the Richardson coefficient with a transmission coefficient, which depends on the barrier height between the silicon and the insulator and the insulator thickness. These two factors are the key parameters that govern the conduction current. In addition, some effects, such as the minority carrier injection, image force, and quantum mechanism reflection, are also neglected. This approximation is only valid for a forward current with V > 3kT/q, because the metal/insulator barrier differs from the silicon/insulator barrier. Some authors have ignored these assumptions and treated the MIS diode as a regular Schottky diode.

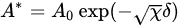

Instead of treating the

n factor as an “ideality factor” in (8), it was proposed that the nonunity

n factor could be calculated from the surface potential of the barrier

[26]. Defining

n as a change in the surface potential, Δ

Vs, with respect to the applied voltage (i.e.,

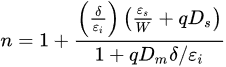

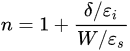

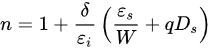

𝑛=−𝑉/Δ𝑉𝑠), and further taking the interface states into consideration, the electrostatic calculation leads to the following:

(10)

where εi and εs are the permittivities of the insulator and semiconductor, respectively; W is the depletion layer in the semiconductor surface; and Ds and Dm are the surface state densities in the equilibrium with the semiconductor and metal, respectively. If the surface state is negligible, (10) reduces to the following:

(11)

Thus, large n values, in some cases, are not mysterious; it is only because the electrostatic thickness of the insulating layer, 𝛿/𝜀𝑖, is much larger than the electrostatic thickness of the depletion layer width, 𝑊/𝜀𝑠. If neglecting the surface states on the metal side, which is the case for most MIS diodes, Equation (10) reduces to the following:

(12)

In this expression, n is a parameter that describes how effectively the barrier surface potential varies with the applied voltage. It has nothing to do with the generation and recombination of carriers or the validity of the Schottky current model. Therefore, it is not an indicator of the ideality of the junction.

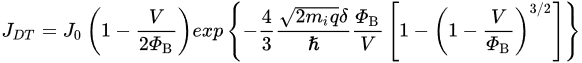

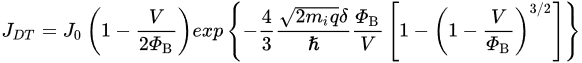

In fact, the validity of (8) for the MIS diode is limited. The conduction current should be more precisely modeled by the direct tunneling current (see Equation (13)) if the insulator layer and barrier height are in the direct tunneling range

[27][28].

(13)

where mi is the electron mass in the oxide; ℏ is the reduced Planck’s constant; and ΦB is the barrier height (in electron volts) between the emitting electrode and the oxide.

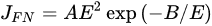

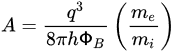

For the case of thicker insulators or with a smaller voltage applied, tunneling over the triangular edge (see

Figure 2c) is also possible. In this situation, the current conduction is better described with the Fowler–Nordheim (FN) equation, as shown below

[29]:

(14)

(15)

(16)

where me is the electron mass in the free space.

The FN formula has been widely used to explain the conduction behavior of various thin dielectric films

[29]. However, in contact studies including the so-called MIS Schottky diode, the current–voltage characteristics were often fitted with the modified Schottky Equation (8) or even the simple Schottky equation in (7) instead of the FN relationship. It has to be pointed out that the barrier height extracted from these fitting should be inaccurate, and the ideality factor does not carry any technical implications. The effective Richardson coefficient is also inappropriate in these cases. The current–voltage characteristics are better described with the FN equation.

3. Ohmic Contact in the Nanoscale

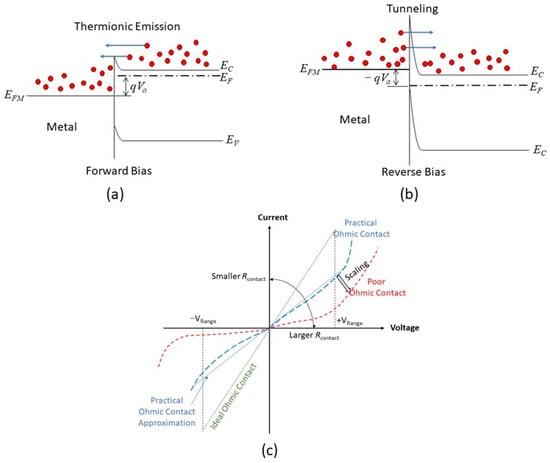

Ohmic contact refers to a metal–semiconductor contact with low and constant resistance regardless of the applied voltage polarity. A low contact resistance and nonrectifying contact enable signals to transmit into and out of a semiconductor device, such as transistors, LEDs, and solar cells, with minimum distortion. Figure 3a,b illustrate the idea for achieving an n-type ohmic contact. A small contact barrier can be obtained by choosing a small metal workfunction. Under forward bias, the electron can be emitted through the barrier via thermionic emission or Schottky emission. With reverse bias (see Figure 3b), the barrier height is increased, but a large reverse current is still possible if the barrier width is narrow enough so that direct tunneling is possible. The ohmic contact has not been considered a server-challenging issue since the start of silicon technology. The key factor governed by the contact resistance can be readily solved with the well-developed metallization and junction doping technique. The narrow barrier is achieved by heavily doping the contact region of the semiconductor. In addition, the junction dimensions, including the cross-sectional area, junction depth, and metal thickness, are quite large compared to the devices themselves. Figure 3c illustrates the ideal ohmic contact’s characteristics, practical ohmic contact, and the scaling effect of the contact. As mentioned, to reduce the signal loss, the contact resistance should be as small as possible. The current–voltage (I–V) relationship in the prescribed voltage range should be linear so that it does not cause signal distribution and harmonics. However, as illustrated in Figure 3a,b, barriers exist in the metal/semiconductor contact; the I–V characteristics are either governed by thermionic emission or tunneling, which are nonlinear. In addition, because the forward and reverse conductions are controlled by different mechanisms, the I–V characteristics are asymmetric. The degrees of nonlinearity and asymmetry may not cause significant issues when the signal levels are high.

Figure 3. Ohmic contact and current-conducting mechanisms: (a) forward bias; (b) reverse bias. (c) Illustration of the current–voltage characteristics of an ideal ohmic contact, practical ohmic contact, and poor ohmic contact that may result from downsizing.

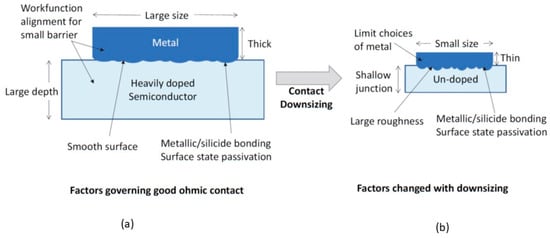

Figure 4 shows the key parameters and process issues for producing a good ohmic contact. Generally, ohmic contact has not been a major challenge in CMOS technology over the past six decades. The contact size is still quite large compared to the conductive current and applied voltage. Moreover, a suitable metal workfunction is available, and the semiconductor can be doped to the degeneracy level. However, in the nano CMOS technology, the situation is changed. To reduce the chip size, every dimension has been scaled down. In the “2 nm” technology, even the power rails of the integrated circuit are scaled and moved to the back side of the IC. Reducing the contact’s cross-sectional area is undoubtedly also an attractive option for fitting more transistors in the chip. Some new technology options, such as the use of high-k gate dielectric materials, will limit the choice of materials for metal gates

[6].

Figure 4. (a) Factors governing the ohmic contact; (b) issues encountered when the device technology scales down to the nanometer range.

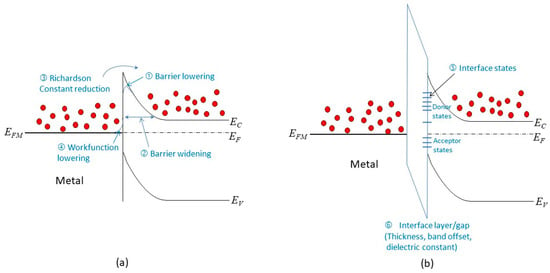

Figure 5 shows how the physics of a Schottky junction and an ohmic contact can be affected by scaling down the junction size. The main effects are as follows:

Figure 5. (a) Possible effects resulting from a scaled metal/semiconductor contact; (b) issues associated with a contact with an interlayer.

- (1)

-

Barrier lowering: The barrier height at the interface can be reduced by various factors, such as image force effects, metal workfunction variation, and surface roughness. These factors may be negligible in a large junction, but they can have significant impacts in a scaled junction. They can increase the forward current by lowering the potential barrier.

- (2)

-

Barrier widening: The use of heavily doped contacts may not be possible in a scaled junction. This can result in a wider tunneling barrier, which reduces the conduction current under reverse bias.

- (3)

-

Richardson constant reduction: Thinner metal films are used in a scaled junction, which can lead to a smaller value of the Richardson constant. This can decrease the forward current by reducing the thermionic emission.

- (4)

-

Metal workfunction lowering: experimental results suggest that thinner metal films have lower workfunctions

[30], which can also reduce the barrier height at the interface.

- (5)

-

Interface states: The presence of interface states can cause Fermi-level pinning, which affects the barrier height and the band bending. This effect is more pronounced in thinner films and in unpassivated surfaces.

- (6)

-

Interface layer: To mitigate the Fermi-level pinning effect or to enable different circuit design options, such as using 2D materials as interlayer conductors, an interface layer may be used for passivation. This can affect the reverse currents by changing the tunneling characteristics. The thickness, band offset, and dielectric constant of the interface layer are important parameters for this effect.

3.1. Effects of Junction Doping

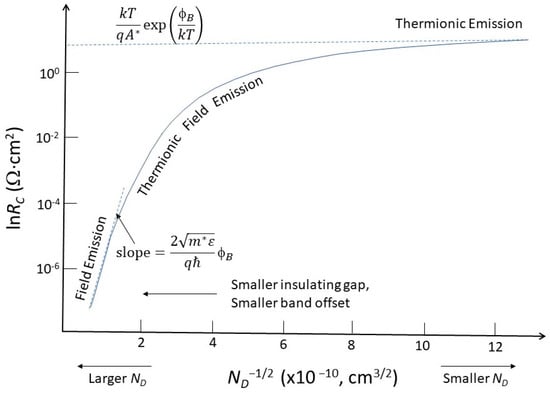

The unavailability of a heavily doped contact results in a wider barrier. As shown in Figure 5a, this reduces the tunneling efficiency. Following the method developed by Yu [31], it can calculate the contact resistance depending on the dopant concentration. Figure 6 shows the contact resistance as a function of the dopant concentration. For high dopant concentrations (>2.5 × 1019 cm−3), the contact resistance decreases to the range of 10−5 to 10−6 Ω-cm2. The current conduction is mainly due to field emission.

Figure 6. Illustration of doping concentration dependence of contact resistance involving different current conduction mechanisms.

3.2. Effects of Interface Roughness

The Schottky current of a metal/semiconductor can exceed the Schottky–Mott limit. Fundamental calculations show that the metal surface flatness affects the electron cloud near it

[32][33]. It was found that the ratio of electric field fluctuations to the average electric field, denoted by δ

E/

ES, can be estimated by the following

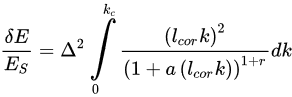

[33]:

(17)

where Es denotes the electric field resulting from a smooth surface; 𝛿 E is the increased electric field due to the surface roughness; k is related to the surface wave vector; Δ is the normalized roughness; lcor is the normalized correlation length; r is the roughness exponent, which is a measure of the degree of surface irregularity; and a is a proportional constant. See Figure 7 for the definitions of the parameters.

Figure 7. Definitions of the key roughness parameters and an illustration of the local averaged thickness variation for small-sized devices as a function of the applied field

[34].

Figure 7 shows how the roughness parameter, Δ, and the correlation length,

lcor, are normalized by the film thickness,

tdiel. The normalized roughness Δ (=r

s/tdiel) becomes more important for films with similar thicknesses. The correlation length, which measures the local field variation, is also inversely related to the film thickness, i.e.,

lcor =

Lcor/

tdiel. This means that thinner films have larger values of Δ and

lcor and, therefore, larger electric field fluctuations

[34].

One of the factors that affect the electrical properties of metal–insulator–metal (MIM) structures is the surface roughness of the interfaces. The lower interface (insulator on metal) tends to be rougher than the upper interface (metal on insulator) due to the crystalline nature and the grain size of the metal films, as well as the limitations of the deposition methods, such as evaporation or sputtering. This phenomenon has been known for decades and persists even in MIM structures with larger dimensions and thicker films

[35][36][37][38][39][40].

The electrical properties of metal/semiconductor contacts strongly depend on the metal film thickness and, also, the method of deposition

[30]. These effects may be partly related to the surface roughness.

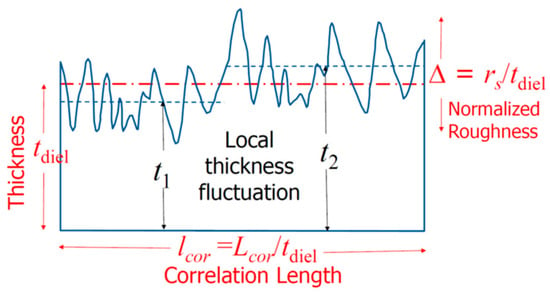

Figure 8 shows how the Schottky barrier height and Richardson constant vary with the metal thickness and deposition process. For an evaporated sample with a 100 Å thickness (see

Figure 8a), the Cu electrode has a barrier height of approximately 0.58 eV and a Richardson constant close to the theoretical value of 112 A/cm

2/K

2. Both parameters increase sharply and reach their saturation values of about twice the theoretical value for the Richardson constant and 0.62 eV for the barrier height for films thicker than 200 Å.

Figure 8. The metal thickness and deposition process are dependent on the Schottky barrier height and Richardson constant: (

a) Cu-Si contacts by evaporation; (

b) sputtered Cu-Si contacts prepared by sputtering. Redrawn based on

[30].

4. Contacts for 2D Materials

Two-dimensional materials, especially transition metal dichalcogenides (TMDs), such as molybdenum disulfide (MoS

2)

[41][42][43], ditelluride (MoTe

2)

[44][45], tungsten diselenide (WSe

2)

[46][47], and phosphorene, are considered to be possible replacements for silicon when silicon-based CMOS devices reach their physical limits

[48][49][50][51][52][53]. These materials, which have high electron mobility, low optical absorption coefficient, and high electrical and thermal conductivities, could enhance the device and circuit performance in many aspects. However, there are still unresolved challenges related to mass production, complex device design, and circuit integration

[48][49].

Most of the reported 2D-material-based devices are currently much bigger than CMOS technology, even though 2D materials are often linked to nanodevices and nanotechnology in the literature. Achieving a good ohmic contact at the submicrometer scale is still a difficult problem. Because the films are only a few monolayers thick and the dopant concentration is far less than that of conventional semiconductors, the contact resistances of metal/2D materials are much larger than that of conventional semiconductors. Shen et al. reported an ultralow resistance ohmic contact based on semi-metallic bismuth on monolayer TMD materials. The Schottky barrier height was reduced to a zero voltage

[54]. There is a large body of literature on 2D-material-based Schottky contact devices from over the last decade

[55][56][57][58][59][60].

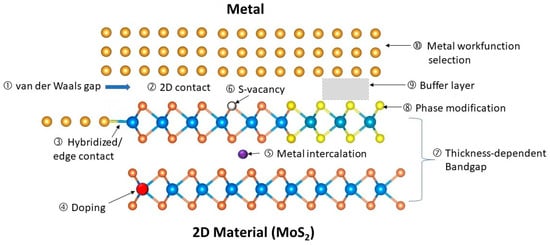

Figure 9 shows the main features and challenges of metal/2D material contacts, which are summarized as follows:

Figure 9. Illustration of the issues and features associated with metal–2D material (MoS2, as an example) contacts.

- (1)

-

van der Waals gap: This is a tunneling barrier between the metal and the 2D material that allows for the tunneling of electrons. Some 2D materials may also form strong bonds with the metal or by overlapping their orbitals.

- (2)

-

2D contact: This is a common method of connecting 2D material from the top, but it has a high resistance per area because the current flows parallel to the 2D plane, not perpendicular to it. A top contact is easier to achieve because it involves depositing metal on the surface of the 2D materials and patterning it with standard photolithography.

- (3)

-

Hybridization and edge contact: This is a better alternative to the 2D contact, as it creates a physical bond and a direct current path along the surface of the 2D material. However, it is challenging to achieve, because it requires the precise alignment and deposition of metal on very thin edges. Some 2D materials may also form strong bonds with the metal or by overlapping their orbitals.

- (4)

-

Doping: 2D materials cannot be doped in the conventional ways, and it is hard to dope heavily.

- (5)

-

Metal intercalation: This is a process of incorporating metal atoms into the gaps of multilayer 2D materials. The dopants contribute to the current’s conduction and can improve the contact’s conductivity.

- (6)

-

Surface defects: These are imperfections, such as sulfur (S) vacancy in MoS2, on the 2D material surface that can trap charges and pin the Fermi level, affecting the contact potential and resistance.

- (7)

-

Layer-dependent bandgap: The bandgap and the contact potential of the 2D material vary with the number of layers. This can be exploited to tune the contact properties by changing the layer thickness in the contact region.

- (8)

-

Phase modification: Some 2D materials can switch among different phases that have distinct electrical properties. For instance, the 2H phase of TMDs is semiconducting, while the 1T and 1T0 phases are metallic. By changing the contact region to a metallic phase, the contact conductivity can be enhanced significantly.

- (9)

-

Buffer layer insertion: inserting a buffer layer between the metal and the 2D material can help reduce the effects of the van der Waals gap and the metal-induced gap states.

- (10)

-

Metal workfunction selection: To achieve good ohmic contact with both n-type and p-type 2D materials, various unconventional metals, such as In, Mg, Ag, Pd, Sc, and Ti, have been explored. However, not much work has addressed the issues of stability, reliability, and potential process contamination. For digital circuit applications, one must consider whether these metals can produce the desired threshold voltages for n-type and p-type transistors.

4.1. Metal van der Waals Contacts and Hybridized Contacts

One of the challenges in fabricating devices based on 2D materials is to ensure a good contact between the 2D lattice and the 3D metal electrodes, without damaging the 2D structure or creating interface defects. To address this issue, some researchers have developed techniques to integrate 3D metal layers with 2D materials using van der Waals (vdWs) forces. These techniques preserve the integrity of the 2D lattice and avoid chemical bonding. For example, Liu et al.

[58] devised a novel method to transfer atomically smooth metal layers onto 2D semiconductors. The procedure involved patterning and depositing the metal layer on an atomically flat Si substrate, then covering it with a PMMA film to enable its detachment. Afterward, a PDMS stamp was employed to lift the PMMA-coated metal layer and align it precisely on the target surface of the 2D material. On the basis of this method, the Schottky barrier height obtained was close to the Schottky–Mott model and had a large pinning factor of 0.96.

From a fabrication process and device operation point of view, there should be a better approach to achieving covalent bonding between 2D materials and metals. An intimate contact would help to eliminate the interfacial tunneling barrier and enhance the carrier injection efficiency. Side or edge contacts on 2D materials are one way to obtain these kinds of metal/2D material contacts. The edge contacts can be fabricated by using either top-down or bottom-up approaches. In a top-down scheme, an insulating layer, such as Al

2O

3 or h-BN, is first deposited on the 2D channel. It is then selectively etched to expose the 2D edges. It was reported that edge-contacted graphene FETs can have a contact resistance as low as 100 Ω·mm while maintaining a high charge carrier mobility

[61].

Some metal/2D material contacts are not thermally stable. The contact characteristics are affected by the interface interaction. McDonnell et al. observed a thin layer of TiO

2 when Ti was deposited on MoS

2 with a vacuum pressure of 10

−6 mbar. This layer was found to have a negligible conduction band offset with MoS

2 and resulted in a low contact resistance

[62]. However, when Ti was deposited in an ultrahigh vacuum of 10

−9 mbar, the Ti atoms reacted with MoS

2, and a Ti

xS

y phase formed, which resulted in a much larger contact resistance. The formation of TiO

2 should be due to the residual oxygen or water molecules in the vacuum system or metal. The thin TiO

2 layer inhibits the direct chemical reaction of Ti and S. At an ultrahigh vacuum, the oxygen and water residuals are significantly reduced, and the direct reaction of Ti and S is possible. Ti

xS

y has poor electrical conductivity. However, Au/MoS

2 contacts were also found to be dependent on the deposition pressure.

To realize CMOS devices with 2D-material-based transistors, achieving both n-type and p-type devices on a single-type 2D material and with the same metal contacts is essential. It was discovered that the polarity of multilayer MoTe

2 encapsulated in h-BN can be varied by applying thermal annealing at different temperatures

[63].

4.2. Junction Doping

High substrate doping has been the key strategy in conventional semiconductor technology to achieve ohmic contacts in CMOS technology. Conventional semiconductors can use different doping techniques, such as ion implantation and plasma immersion ion implantation

[1], to increase the doping concentration to a degeneracy level. However, these methods are not compatible with 2D materials that have only a few atomic layers. A more effective doping method for 2D materials is spontaneous charge transfer doping (SCTD)

[64][65]. For p-type doping, the energy difference between the top of the valance band of the 2D material and the lowest unoccupied molecular orbital (LUMO) of the surface doping will cause electron transfer, which leads to hole accumulation and the lifting upward of the valence band in the semiconductor surface region. Similarly, suppose the bottom of the conduction band of the 2D material is below the highest occupied molecular orbital (HOMO) of the surface dopant; electrons will transfer from the HOMO of the surface dopant to the conduction band of the semiconductor and result in the electron doping. A wide range of dopants for various 2D materials are available

[64].

4.3. Bandgap Modification and Band Alignment

Band alignment can be achieved by selecting a metal with a suitable workfunction. Previous studies have shown that the contact potential depends on the type of surface termination

[66]. For top contacts with a monolayer of MoS

2, the Fermi-level pinning is close to the conduction band edge, and n-type Schottky barriers are formed. In this case, Al, In, and Mg may be good candidates for ohmic contacts. The edge contacts, either armchair or zigzag termination of Mo and S atoms, result in a Fermi-level pinning near the valence band, and p-type Schottky barriers are formed.

Two-dimensional material has a distinct nature in that the bandgap can be readily tuned by stacking a different number of 2D monolayers. The bandgaps of 2D materials vary with the number of layers and their stacking configurations, which influences the quantum confinement effects. On the basis of the first-principles calculations, Wickramaratne et al. found that the band gap of a single monolayer of hexagonal boron nitride (h-BN) is a direct bandgap semiconductor; the gap becomes indirect for multiple layers

[67]. The positions of the band edges, with respect to the vacuum level, shift by 0.5 eV for the direct-to-indirect transition. Thickness-dependent bandgap characteristics were also found in other 2D materials.

4.4. Phase Modification

Two-dimensional materials can exist in different crystal structures or phases. Different phases have different electronic and optical properties and, thus, different metal contact behaviors as well

[68][69]. For example, 2H-TMDs are semiconducting materials with a trigonal prismatic structure, while 1T and 1T0 phases are metallic materials with an octahedral structure. Using n-butyllithium to induce a phase transition from 2H to 1T’ or 1T0 in a MoS

2 nanosheet, Kappera et al. achieved a significant reduction in contact resistance to 0.24 kΩ⋅μm

[69].

4.5. Fermi-Level Pinning and Buffer Layer

The interface states at two-dimensional material/metal interfaces can affect the performance of two-dimensional devices. These states include metal-induced gap states (MIGS) and defect states, which can induce Fermi-level pinning (FLP) at the interface and hinder the carrier injection efficiency. Fermi-level pinning causes adverse effects in 2D material/metal contacts. It was proposed to be one of the main reasons for the experimental observations of large contact resistance. The origins of the FLP effect at the 2D material/metal interface should be due to several causes.

A buffer layer can reduce the effects of metal-induced gap states (MIGS) by creating a matching layer between the 2D material and the metal. This idea was inspired by previous work on high-performance metal–insulator–semiconductor (MIS) diodes

[17][26]. The buffer layer prevents the metal wave function from penetrating the semiconductor material, which lowers the MIGS density. Moreover, if the buffer layer is an insulator, it can balance the charge at the interface and shift the Fermi-level closer to the charge neutrality level, which further decreases the effective Schottky barrier height.

One of the most often used buffer materials for 2D material/metal contacts is graphene. Graphene has a semi-metallic nature and a tunable workfunction. By inserting prepatterned single-layer graphene between MoS

2 and metal, Chee and co-workers created a sandwich contact structure for MoS

2 FETs

[70]. The graphene layer enhanced the contact between MoS

2 and Ag significantly. The Schottky barrier height was reduced to 190 meV due to the charge transfer from Ag to graphene that matched the Fermi level of graphene with a conduction band edge of MoS

2. This increased the electron mobility by almost three times. Graphene is not the only metallic 2D material that can act as an interfacial buffer layer to achieve ohmic contacts for 2D-material-based devices.

5. 2D Contact with Silicon

The current 2D-material-based electron devices are still much larger than state-of-the-art CMOS technology. There is a lack of mass production and large-scale integration technology for these devices. Therefore, it is unlikely that 2D-material-based ICs will replace the mainstream silicon technology in the next ten years. However, it is highly possible that some 2D materials will be integrated with Si technology to overcome some of the limitations of CMOS devices and fabrication technology and to enhance the performance of silicon devices. For instance, using 2D materials instead of the expensive indium tin oxide (ITO) films in photonic devices could be a promising option for 2D materials/Si technology integration. Graphene–silicon solar cells have been extensively studied since the discovery of graphene

[71][72][73]. However, some fundamental issues of the graphene/silicon interface are still not well understood. Some puzzling issues, such as the wide variations in Schottky barrier height and large fluctuations in the ideality factor (from ~1 to 30), were observed in this simple structure

[25][74]. These wide ranges in parameter values suggest that some additional physical mechanisms in addition to the Schottky emission should be considered.

The interface between 2D material and silicon has a unique nature that is not common in the conventional silicon process and is also unknown to the 2D material community

[25]. Two-dimensional materials, such as graphene, have a much lower surface defect density than most conventional semiconductor materials. However, silicon has many dangling bonds on its surface. The van der Waals contact of the graphene/Si interface would leave a large number of unpassivated silicon dangling bonds.