Your browser does not fully support modern features. Please upgrade for a smoother experience.

Submitted Successfully!

Thank you for your contribution! You can also upload a video entry or images related to this topic.

For video creation, please contact our Academic Video Service.

Video Upload Options

We provide professional Academic Video Service to translate complex research into visually appealing presentations. Would you like to try it?

Cite

If you have any further questions, please contact Encyclopedia Editorial Office.

Gu, L.; Hu, S.; , .; Lujun Lin, L.L. Ka-Band Power Amplifier. Encyclopedia. Available online: https://encyclopedia.pub/entry/21374 (accessed on 08 May 2026).

Gu L, Hu S, , Lujun Lin LL. Ka-Band Power Amplifier. Encyclopedia. Available at: https://encyclopedia.pub/entry/21374. Accessed May 08, 2026.

Gu, Ling, Shanwen Hu, , Lujun Lin Lujun Lin. "Ka-Band Power Amplifier" Encyclopedia, https://encyclopedia.pub/entry/21374 (accessed May 08, 2026).

Gu, L., Hu, S., , ., & Lujun Lin, L.L. (2022, April 06). Ka-Band Power Amplifier. In Encyclopedia. https://encyclopedia.pub/entry/21374

Gu, Ling, et al. "Ka-Band Power Amplifier." Encyclopedia. Web. 06 April, 2022.

Copy Citation

With the increase in the demand for high-speed transmission communication, satellite communication is developing rapidly. Because of the bandwidth capacity, the K/Ka band is considered the mainstream frequency band of satellite communication. The performance of a power amplifier (PA) directly affects the power of the transmitter, so the application of a power amplifier in Ka-band satellite communication is very important.

power amplifier

Ka band

satellite communication

1. Introduction

Satellite communication has the characteristics of wide coverage, large capacity, and long communication distance, and is not limited by the geographical environment. It is widely applied in broadband multimedia communications, personal mobile communications, military communication, and other fields. In the long-term development process, satellite communication and mobile communication form complementary relationships, playing an irreplaceable role [1].

At present, the frequency bands used in satellite communication mainly include the L band, S band, C band, Ku band, and Ka band. In the past decade, with the continuous development of the satellite application field, spectrum congestion has occurred in the conventional frequency bands L band, S band, and C band allocated by satellite services [2]. Limited by bandwidth, the communication rate of these satellites is becoming more and more difficult to meet the needs of information society for high-speed data transmission. In this case, Ka-band broadband communication satellite technology has entered the field of vision of various countries and become the research goal of various countries because of the wide available frequency band (26.5 GHz~40 GHz) and few interference signals.

In 1997, the U.S. Federal Communications Commission (FCC) issued Ka-band satellite communication licenses to more than a dozen companies to promote the development of Ka-band satellite communication technology. These high-tech companies include Motorola’s Celestri system, Lockheed Martin’s Astrolink system, GE Americom’s Ge star system, and others [3]. After years of development, the Ka-band broadband multimedia communication satellite in the United States has been put into commercial use, which can provide high-speed broadband Internet access services for rural families in remote areas and airliners.

Because the rain attenuation of the Ka band is greater than that of the Ku band, the requirements for devices and processes are higher, and satellite communication in the Ka band developed slowly in the past [4]. With the improvement in the hardware manufacturing level, Ka-band microwave circuits have developed rapidly over the past 10 years.

In October 2011, the full Ka-band communication satellite ViaSat-1 of VIASAT was successfully launched [5]. The total communication capacity of ViaSat-1 exceeds 140 Gbps, which is more than 70 times that of any Ku-band satellite at that time [6]. In particular, with the launch of the new generation satellite ViaSat-1, the concept of the high price and narrow bandwidth of traditional satellites has been changed. The transmission speed provided by the satellite is higher than that of terrestrial digital subscriber line DSL and wired cable, but the service price of users is almost the same [7]. In 2012, ViaSat-1 was officially put into commercial use, opening a new era of Ka-band satellite communication [8].

In addition to the field of satellite communication, the next generation mobile communication technology 5G is also likely to use the communication technology of the Ka band. Regarding 5G, the Third-Generation Partnership Project (3GPP) determined the millimeter-wave band 26 GHz/28 GHz/39 GHz as the 5G band to be deployed first in the world [9].

In recent years, many high-tech companies in the United States and South Korea have successively completed the verification test of the 5G communication prototype based on a 28 GHz band [10]. Whether for 5G or broadband communication satellites in the future, Ka-band applications can provide high-speed communication services. With the maturity and promotion of these technologies, there will be a lot of demand for Ka-band communication systems in the future.

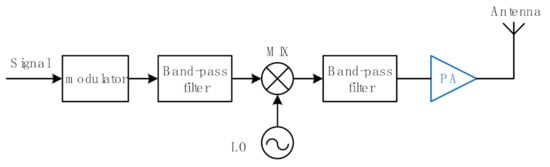

As an important part of the transmitter in the communication system, the performance of the power amplifier plays a decisive role in the performance of the whole system. Figure 1 is a block diagram of a communication system transmitter. Usually, the power amplifier is located at the end of the transmitter of the whole communication system. After the signal passes through the modulator, mixer, and band-pass filter, it is amplified to a certain power level through the power amplifier and transmitted through the antenna. Among these modules of the communication system, the power amplifier is a core module. Its linearity directly determines the transmission signal quality of the transmitter, its efficiency determines the power consumption of the transceiver, and its output power determines the distance of communication. Therefore, designing a power amplifier with good performance is the key to determine the quality of wireless communication. Therefore, the research of the power amplifier is very important.

Figure 1. A block diagram of a communication system transmitter.

2. Technology

There are several semiconductor processes that have been demonstrated for power amplifiers at the Ka band. They are gallium arsenide pseudomorphic high electron mobility transistors (GaAs pHEMT) [11], gallium nitride high electron mobility transistors (GaN HEMT) [12], indium phosphide heterojunction bipolar transistor (InP HBT) [13], silicon complementary metal–oxide–semiconductor (Si CMOS) [14], silicon and germanium bipolar complementary metal–oxide–semiconductor (SiGe BiCMOS) [15] and silicon on insulator complementary metal–oxide–semiconductor (SOI CMOS) [16].

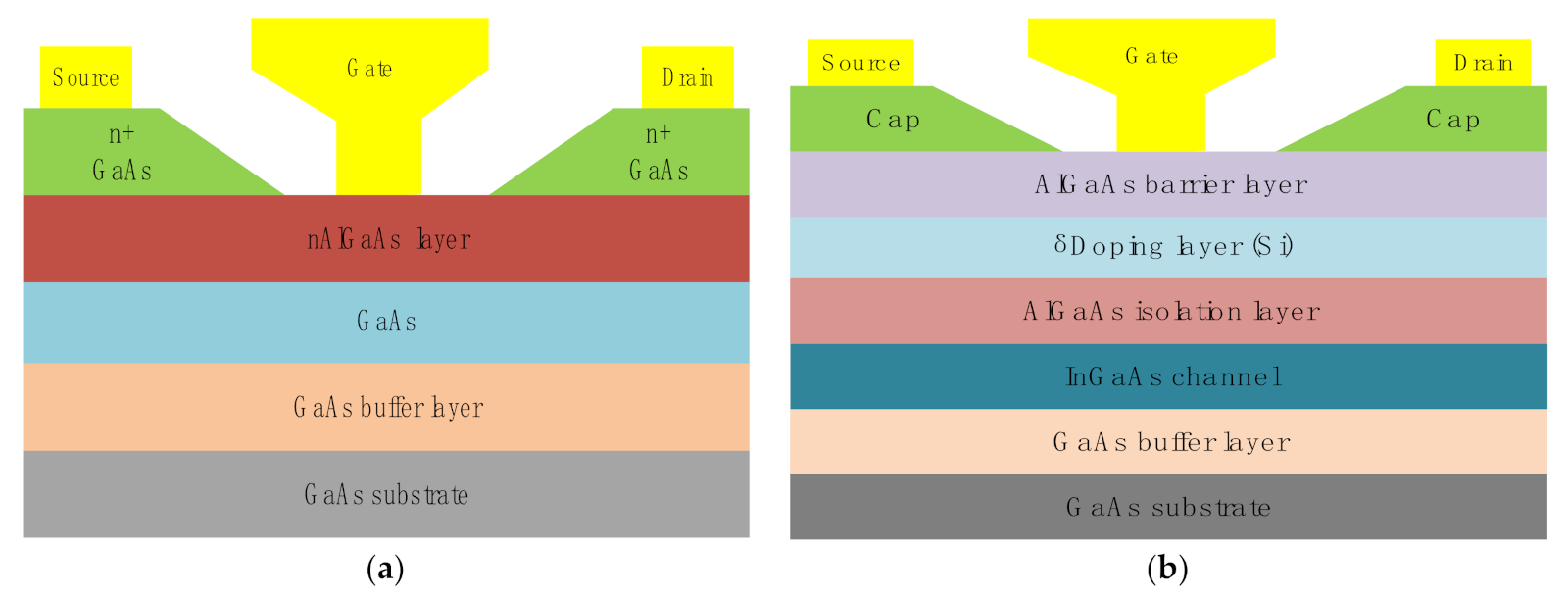

In the late 1970s and early 1980s, the HEMT structure was proposed and developed [17][18]. During this period, a number of research groups around the world proposed the AlGaAs/GaAs crystal structure, collectively known as HEMT. The traditional GaAs HEMT structure profile is shown in Figure 2a [19].

Figure 2. (a)Traditional GaAs HEMT structure profile, (b) GaAs pHEMT structure.

However, there exists a deep donor state trap DX center in the AlGaAs/GaAs heterojunction, which causes device degradation at low temperatures [20]. To solve this problem, Phemt was invented.

In 1986, A. Ketterson first fabricated the AlGaAs/InGaAs/GaAs Phemt structure on a GaAs substrate [21]. The GaAs Phemt structure is shown in Figure 2b.

GaAs Phemt solves the above problems by introducing the AlGaAs isolation layer, which is used to isolate the two-dimensional electron gas (2DEG) layer and doping layer [22]. Compared to HEMT devices, Phemt greatly improves electronic transport characteristics. The electron mobility velocity of GaAs is 5 or 6 times that of Si and has higher drift velocity and better high frequency characteristics [23]. In recent years, Phemt’s cut-off frequency fT

and maximum frequency fMAX reached 360 GHz and 400 GHz, and they are widely used in millimeter-wave frequencies [24]. However, GaAs has high thermal resistance and low breakdown voltage, which limits its application in high voltage and high power. In 2018, Aviv Barabi presented a PA targeting more than 25 Db gain and 27.3 dBm output power between 96 and 98 GHz adopting 0.1 μm GaAs Phemt [25]. In 2020, Ref. [26] proposed a 3-stage CS PA in 65 nm CMOS, achieving 13.4 dBm saturated output power (Psat

) with peak PAE of 11.3% in the 85–101 GHz range. Compared with CMOS process, the GaAs process has the advantage of high output power at higher frequency.

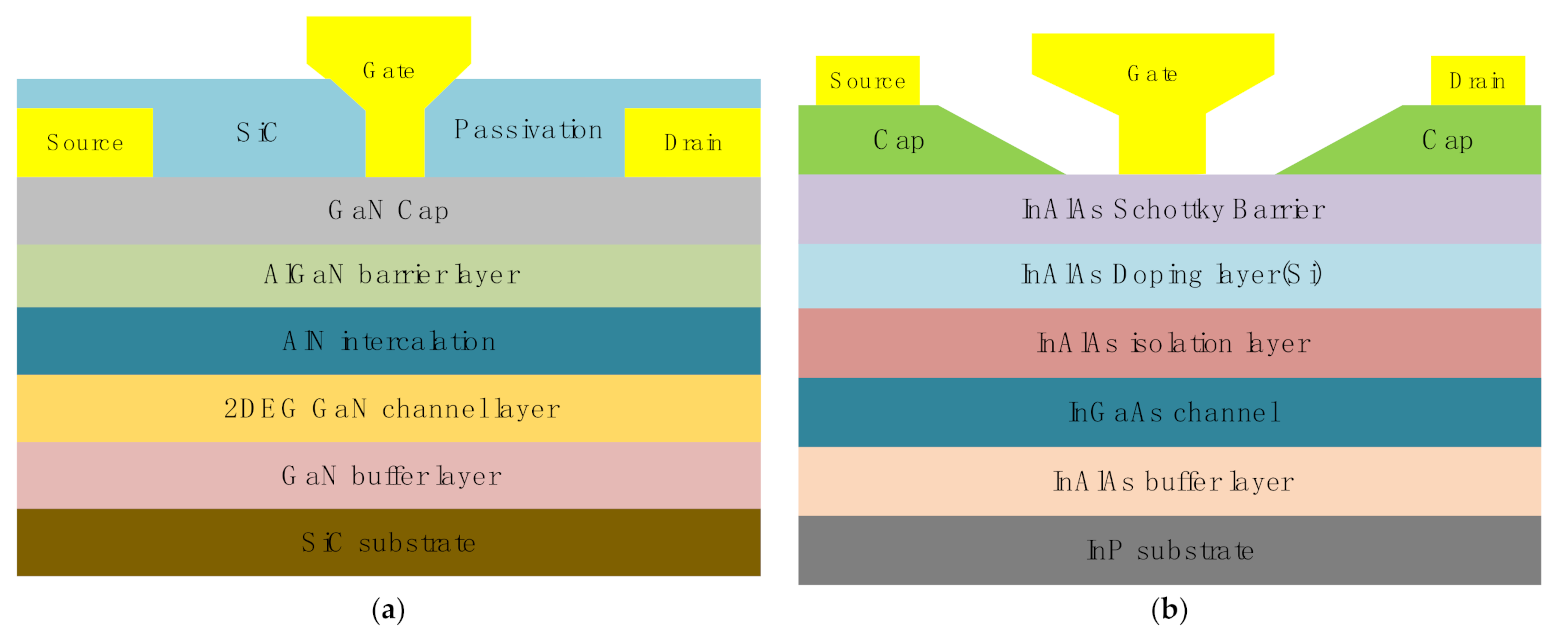

GaN HEMT and GaAs Phemt devices operate on a similar principle and are both high electron mobility transistors operating through 2DEG [27]. However, due to GaN’s special spontaneous polarization, GaN HEMT can also produce 2DEG without doping. The profile of GaN HEMT is shown in Figure 3a.

Figure 3. (a) GaN HEMT structure profile, (b) InP HEMT structure profile.

Figure 3. (a) GaN HEMT structure profile, (b) InP HEMT structure profile.GaN and GaAs have similar frequency characteristics, but due to the special spontaneous polarization of GaN, the concentration of 2DEG is one order of magnitude higher than that of GaAs [28]. Therefore, GaN has high current density and outputs high power at high frequency. In 2018, M. Roberg presented a GaN MMIC Pas using Qorvo’s QgaN15 released process. The output power of the reported PA is approximately 46.2 dBm at 27.5–29.5 GHz [29]. The substrate selection of GaN is a key problem. GaN devices grown on a SiC substrate can obtain higher performance, but the cost is very high. Therefore, several research groups regard GaN on the Si substrate as a feasible solution for the large-scale market application, and massive commercial products have been designed and manufactured. However, compared with the SiC substrate, the Si substrate has worse electrical and thermal properties [30]. The cost and performance must be considered comprehensively to select a more appropriate scheme. In a word, the GaN process can bring some advantages of III-V technology (III-V compound semiconductor technologies include GaAs, GaN, InP, etc.) and its price is lower than the GaAs technology due to the possibility of integration on the Si substrate.

In the research of high frequency electronic devices, the transistors using InP materials are adopted in HEMT and HBT technology. The InP HEMT device is a vertical device, which has better noise characteristics than the InP HBT device. It is often used to design low-noise amplifiers. Its profile is shown in Figure 3b.The InP HBT device is a transverse device. Compared with InP HEMT, its breakdown voltage is higher, and its power capacity is larger. It is often used to design power amplifiers.

InP HBT is mainly divided into a single heterojunction bipolar transistor (SHBT) and a double heterojunction bipolar transistor (DHBT). On the one hand, the band gap of the InP DHBT collector material is greater than that of the InP SHBT collector material, so its collector has higher voltage resistance, and it is conducive to high power output; on the other hand, the collector material of InP DHBT has high thermal conductivity, so it has better heat dissipation performance and is more suitable for high-current and high-power circuit design.

InP-based technology is the only technology that can provide Pas with >20 dbm output power over 200 GHz [31][32]. DHBT 500 nm and 250 nm technology nodes provide about 330 GHz and 400 GHz fT

respectively, and the latter’s up to 700 Ghz. Compared with traditional CMOS FET, the InP DHBT process has the advantages of large breakdown voltage, small parasitic capacitance and low substrate loss. The main limitation of InP is its cost because it is difficult to purchase and is a very fragile material, which makes its manufacturing and handling extremely dangerous.

With the increase in the operating frequency of Pas, the CMOS process node decreases to several nanometers or tens of nanometers [33]. The reduction in the MOS transistor size will reduce the breakdown voltage threshold of the gate oxide layer, and the power supply voltage will also decrease with the increase in the process nodes. Silicon has low electron mobility and poor high frequency characteristics, which limits the application of silicon technology in the higher frequency band. The lower breakdown voltage also limits the output power of the power amplifier.

However, due to the extremely rich content of silicon in nature, it is easy to purify and grow a single product. The cost of silicon technology is much lower than that of III-V technologies (when mass produced). In addition, the integration of silicon technology is very high, and multi-layer metal layers can make very complex circuits. In 2021, J. Park proposed a 2-stage cascode PA in 60 nm CMOS. The PA achieved 17.1 dBm output power and the PAE remained above 38.2% in the area of 0.16 mm2 [34]. When the performance requirements are not too strict, the silicon process can be realized in a small area, and the cost is very low. Therefore, silicon technology is one of the important processes for making the Ka-band power amplifier.

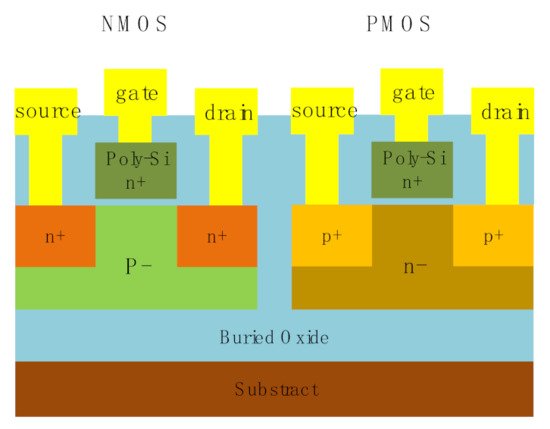

With decades of development, bulk silicon CMOS technology has become more and more mature. However, with the continuous reduction in device feature size, many new problems still appear, such as the short channel effect. SOI (silicon on insulator) technology refers to the process of forming a layer of semiconductor monocrystalline silicon thin film material on the insulating material layer, and then manufacturing integrated circuits on monocrystalline silicon. The main difference between the traditional bulk CMOS process and SOI technology is that SOI CMOS have a buried oxide layer, which separates the device from the substrate [35]. Its profile is shown in Figure 4. In SOI CMOS, each device is surrounded by an oxide layer, which is completely isolated from the surrounding devices and fundamentally eliminates the latch-up effect [36]. At the same time, the buried oxygen layer also increases the thickness of the insulating layer between the interconnect and the substrate, which greatly reduces the parasitic capacitance of the interconnect [37]. Reducing the capacitance is helpful to improve the speed of the circuit and reduce the power consumption of the circuit. IBM 45 nm CMOS SOI technology has been widely used in the development of millimeter-wave power amplifiers [38][39][40]. It provides SOI CMOS transistors with very high >400 GHz) [41]. The excellent performance of SOI MOSFET makes the SOI CMOS circuit more suitable for working in harsh environments, such as aerospace and high temperature.

Figure 4. SOI CMOS structure profile.

However, SOI CMOS process technology cannot replace bulk silicon CMOS technology, mainly because the SOI CMOS process is not as mature as the bulk silicon CMOS process. The quality of the silicon film of SOI material is not as good as that of bulk silicon material. In addition, the cost of SOI CMOS is higher than that of bulk silicon CMOS.

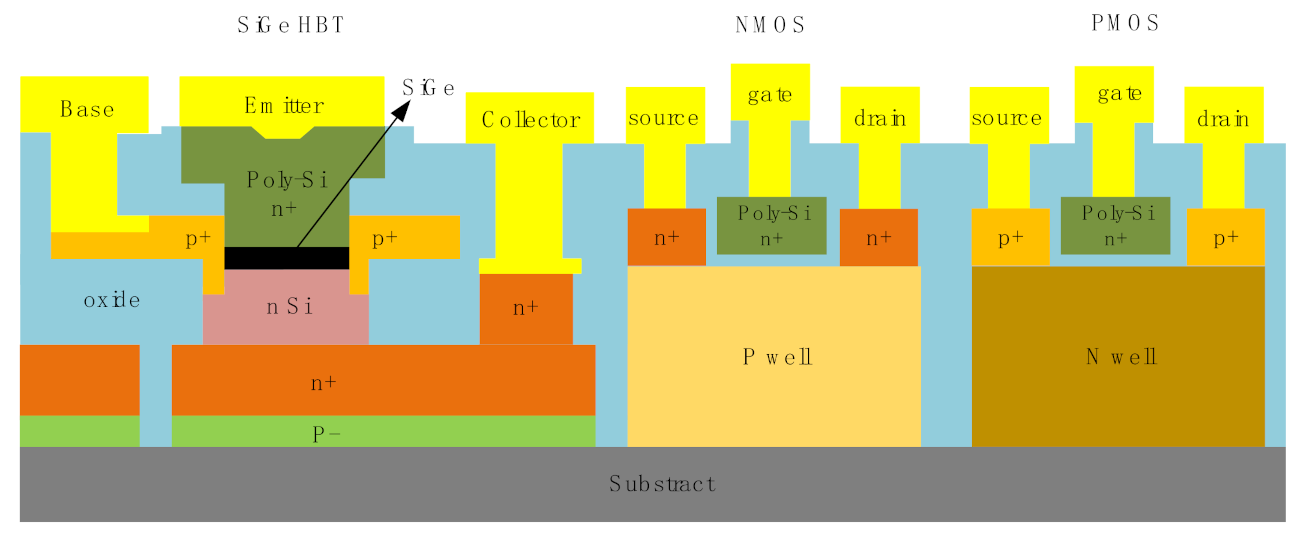

The development of SiGe devices is mainly promoted by IBM and other companies. The BiCMOS process is adopted, which can be used as an alternative to CMOS. BiCMOS technology is a new technology that integrates bipolar transistor (BJT) and field-effect transistors (FET) on the same chip. Compared with CMOS, under the same scale, the performance and cut-off frequency of the SiGe device are greatly improved, and it is better than the silicon-based CMOS device in withstanding voltage and the current processing ability, so it is also suitable for medium power applications. As shown in Figure 5, SiGe BiCMOS combines SiGe HBT applied to the RF circuit and SiGe CMOS applied to digital circuit, combining the digital and analog on one chip. Compared with traditional Si BiCMOS, SiGe BiCMOS is more conducive to integration. In the past 10 years, SiGe BiCMOS technology has been greatly developed, breaking through the technical barriers of 0.35, 0.18 and 0.13 um. The cut-off frequency fT

of SiGe HBT has reached 40~350 GHz, and the maximum operating frequency can almost reach the level of GaAs [42]. It has strong competitiveness and wide application prospects in the RF field.

Figure 5. SiGe BiCMOS structure profile.

GaN and GaAs materials have power advantages for chips with an operating frequency not higher than 100 GHz. If frequency is the primary consideration of the device, the frequency of the power amplifier made of the InP device can be higher than 500 GHz. Of course, for industrial manufacturing, the product cost is also an important factor in the power amplifier design and mass production. Especially for consumer electronics, CMOS is conducive to system-on-chip integration, so it has a cost advantage. In addition, the loss of performance or quality factors of passive components are quite competitive [43].

References

- Xu, X.; Wang, N.; Wang, C. Reflection on the Development of Satellite Communications and the Integration with Terrestrial Mobile Communications. Aerosp. China 2021, 22, 59–66.

- Panagopoulos, A.D.; Arapoglou, P.; Cottis, P.G. Satellite communications at KU, KA, and V bands: Propagation impairments and mitigation techniques. Commun. Surv. Tutor. IEEE 2004, 6, 2–14.

- Evans, J.V.; Proposed, U.S. Global satellite systems operating at Ka-Band. In Proceedings of the Aerospace Conference, Snowmass, CO, USA, 28–28 March 1998.

- Hasanuddin, Z.B.; Fujisaki, K.; Ishida, K.; Tateiba, M. Measurement of Ku-band rain attenuation using several VSATs in Kyushu Island, Japan. IEEE Antennas Wirel. Propag. Lett. 2002, 1, 116–119.

- ViaSat-1 Led the Innovation of a New Class of Ka-Band Satellite Systems. Available online: http://www.viasat.com (accessed on 24 October 2021).

- High-Capacity Satellite System and ViaSat-1. Available online: https://www.viasat.com/space-innovation/satellite-fleet/viasat-1/ (accessed on 24 October 2021).

- ViaSat-1. Available online: http://www.ssloral.com (accessed on 24 October 2021).

- Deng, H.; Fei, P.; Yuan, J.; Shen, Y.; Pan, J. High Throughput Satellite System Capacity Analysis and Application Forecast. China Aerosp. 2016, 17, 30–40.

- Standard 3GPP Std.release 15; 3GPP 5G Mobile Broadband Standard Release 15. Available online: https://www.3gpp.org/release-15 (accessed on 26 October 2021).

- Sung, M.; Cho, S.-H.; Kim, J.; Lee, J.K.; Lee, J.H.; Chung, H.S. Demonstration of IFoF-Based Mobile Fronthaul in 5G Prototype With 28-GHz Millimeter wave. J. Lightwave Technol. 2018, 36, 601–609.

- Gunnarsson, S.E.; Karnfelt, C.; Zirath, H.; Kozhuharov, R.; Kuylenstierna, D.; Alping, A.; Fager, C. Highly integrated 60 GHz transmitter and receiver MMICs in a GaAs pHEMT technology. IEEE J. Solid-State Circuits 2005, 40, 2174–2186.

- Shinohara, K.; Regan, D.C.; Tang, Y.; Corrion, A.L.; Brown, D.F.; Wong, J.C.; Robinson, J.F.; Fung, H.H.; Schmitz, A.; Oh, T.C.; et al. Scaling of GaN HEMTs and Schottky Diodes for Submillimeter-Wave MMIC Applications. IEEE Trans. Electron Devices 2013, 60, 2982–2996.

- Hamada, H.; Tsutsumi, T.; Matsuzaki, H.; Sugiyama, H.; Nosaka, H. 475-GHz 20-dB-Gain InP-HEMT Power Amplifier Using Neutralized Common-Source Architecture. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020.

- Iwai, H. Future of nano CMOS technology. Solid-State Electron. 2015, 112, 56–67.

- Harame, D.L.; Ahlgren, D.C.; Coolbaugh, D.D.; Dunn, J.S.; Freeman, G.G.; Gillis, J.D.; Groves, R.A.; Hendersen, G.N.; Johnson, R.A.; Joseph, A.J.; et al. Current status and future trends of SiGe BiCMOS technology. IEEE Trans. Electron Device 2001, 48, 2575–2594.

- Flandre, D.; Raskin, J.P.; Vanhoenacker-Janvier, D. Soi Cmos Transistors for RF and Microwave Applications. Int. J. High Speed Electron. Syst. 2001, 11, 1159–1248.

- Yonezu, H.; Kobayashi, K.; Minemura, K.; Sakuma, I. GaAs-Al x Ga 1-x as double heterostructure laser for optical fiber communication system. In Proceedings of the 1973 International Electron Devices Meeting, Washington, DC, USA, 3–5 December 1973.

- Cho, A.; Casey, H. Molecular beam epitaxy: A technique for growth of GaAs-AlxGa1-xAs heterostructure lasers. IEEE J. Quantum Electron. 1974, 10, 791.

- Lavanga, S.; Chini, A.; Coppa, A.; Corsaro, F.; Nanni, A.; Pantellini, A.; Romanini, P.; Lanzieri, C. High Voltage Breakdown pHEMTs for C-band HPA. In Proceedings of the Microwave Integrated Circuits Conference, Paris, France, 27–28 September 2010.

- Lang, D.V.; Logan, R.A.; Jaros, M. Trapping characteristics and a donor-complex (DX) model for the persistent-photoconductivity trapping center in Te-doped Al × Gal- ×As. Phys. Rev. B 1979, 19, 1015.

- Ketterson, A.A.; Masselink, W.T.; Gedymin, J.S.; Klem, J.; Peng, C.-K.; Kopp, W.F.; Morkoc, F.; Gleason, K.R. Characterization of InGaAs/AlGaAs pseudomorphic modulation-doped field-effect transistors. IEEE Trans. Electron Devices 1986, 33, 564–571.

- Li, X.J.; Ao, J.P.; Wang, R.; Liu, W.-J.; Wang, Z.-G.; Zeng, Q.-M.; Liu, S.-Y.; Liang, C.-G. An 850 nm wavelength monolithic integrated photoreceiver with a single-power-supplied transimpedance amplifier based on GaAs PHEMT technology. In Proceedings of the GaAs IC Symposium. IEEE Gallium Arsenide Integrated Circuit Symposium, 23rd Annual Technical Digest 2001 (Cat. No.01CH37191), Baltimore, MD, USA, 21–24 October 2001.

- Yung, Y.S. A tutorial on GaAs vs silicon. In Proceedings of the IEEE International Asic Conference & Exhibit, Rochester, NY, USA, 21–25 September 1992.

- Chien, F.-T.; Lin, D.-W.; Yang, C.-W.; Fu, J.S.; Chiu, H.-C. A low insertion loss GaAs pHEMT switch utilizing dual n+-doping AlAs etching stop layers design. Solid State Electron. 2010, 54, 231–234.

- Barabi, A.; Ross, N.; Wolfman, A.; Shaham, O.; Socher, E. A +27 dbm psat 27 db gain w-band power amplifier in 0.1 μm gaas. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium—IMS, Philadelphia, PA, USA, 10–15 June 2018.

- Elazar, T.; Socher, E. 95GHz 13dBm IQ-combined PA in 65nm CMOS. In Proceedings of the 2020 50th European Microwave Conference (EuMC), Utrecht, The Netherlands, 12–14 January 2021.

- Kumazaki, Y.; Ohki, T.; Kotani, J.; Ozaki, S.; Niida, Y.; Makiyama, K.; Minoura, Y.; Okamoto, N.; Nakamura, N.; Watanabe, K. Remarkable Current Collapse Suppression in GaN HEMTs on Free-standing GaN Substrates. In Proceedings of the 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA, 3–6 November 2019.

- Shur, M.S. GaN based transistors for high power applications. Solid-State Electron. 1998, 42, 2131–2138.

- Roberg, M.; Kywe, T.; Irvine, M.; Marrufo, O.; Nayak, S. 40 W Ka-Band Single and Dual Output GaN MMIC Power Amplifiers on SiC. In Proceedings of the IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium, San Diego, CA, USA, 15–17 October 2018.

- Liao, M.; Shen, B.; Wang, Z. (Eds.) Ultra-Wide Bandgap Semiconductor Materials; Elsevier: Amsterdam, The Netherlands, 2019.

- Griffith, Z.; Urteaga, M.; Rowell, P. 180–265 GHz, 17–24 dBm output power broadband, high-gain power amplifiers in InP HBT. In Proceedings of the 2017 IEEE/MTT-S International Microwave Symposium—IMS, Honololu, HI, USA, 4–9 June 2017.

- Griffith, Z.; Urteaga, M.; Rowell, P. 190-260GHz High-Power, Broadband PA’s in 250nm InP HBT. In Proceedings of the Compound Semiconductor Integrated Circuit Symposium. IEEE, Honololu, HI, USA, 4–9 June 2017.

- Rizvi, A.; Jaiswal, P. Review on Present Trends in CMOS Scaling Technologies. Int. J. Sci. Eng. Technol. Res. 2016, 5, 953–956.

- Park, J.; Kang, S.; Hong, S. Design of a Ka-Band Cascode Power Amplifier Linearized with Cold-FET Interstage Matching Network. IEEE Trans. Microwave Theory Tech. 2021, 69, 1429–1438.

- Adan, A.O.; Naka, T.; Kagisawa, A.; Shimizu, H. SOI as a mainstream IC technology. In Proceedings of the IEEE International Soi Conference, Stuart, FL, USA, 5–8 October 1998.

- Truyen, D.; Leduc, E.; Braud, F. Elimination of Single Event Latch-Up in the ATMEL ATMX150RHA Rad-Hard CMOS 150nm Cell-Based ASIC Family. In Proceedings of the 2015 15th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Moscow, Russia, 14–18 September 2015.

- Udrea, F.; Popescu, A.; Milne, W. Breakdown analysis in JI, SOI and partial SOI power structures. In Proceedings of the IEEE International Soi Conference, Fish Camp, CA, USA, 6–9 October 1997.

- Sarkas, I.; Balteanu, A.; Dacquay, E.; Tomkins, A.; Voinigescu, S. A 45nm SOI CMOS Class-D mm-Wave PA with >10Vpp differential swing. In Proceedings of the Solid-state Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 19–23 February 2012.

- Bhat, R.; Chakrabarti, A.; Krishnaswamy, H. Large-scale power-combining and linearization in watt-class mmWave CMOS power amplifiers. In Proceedings of the Radio Frequency Integrated Circuits Symposium (RFIC), Seattle, WA, USA, 2–4 June 2013.

- Chakrabarti, A.; Krishnaswamy, H. High power, high efficiency stacked mmWave Class-E-like power amplifiers in 45nm SOI CMOS. In Proceedings of the Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 9–12 September 2012.

- Inac, O.; Uzunkol, M.; Rebeiz, G.M. 45-nm CMOS SOI Technology Characterization for Millimeter-Wave Applications. IEEE Trans. Microw. Theory Tech. 2014, 62, 1301–1311.

- Lee, S.H.; Lee, J.Y.; Kim, S.H.; Bae, H.-C.; Lee, S.-Y.; Kang, J.-Y.; Kim, B.W. A 5.8 GHz MMIC Down-Conversion Mixer for DSRC Receiver using SiGe BiCMOS Process. In Proceedings of the 2005 Asia-Pacific Conference on Communications, Perth, WA, Australia, 5 October 2005.

- Pekarik, J.J.; Adkisson, J.; Gray, P.; Liu, Q.; Camillo-Castillo, R.; Khater, M.; Jain, V.; Zetterlund, B.; DiVergilio, A.; Tian, X.; et al. A 90nm SiGe BiCMOS technology for mm-wave and high-performance analog applications. In Proceedings of the Bipolar BiCMOS Circuites and Technology Meeting, Coronado, CA, USA, 28 September–1 October 2014.

More

Information

Subjects:

Engineering, Electrical & Electronic

Contributors

MDPI registered users' name will be linked to their SciProfiles pages. To register with us, please refer to https://encyclopedia.pub/register

:

View Times:

1.1K

Revisions:

2 times

(View History)

Update Date:

06 Apr 2022

Notice

You are not a member of the advisory board for this topic. If you want to update advisory board member profile, please contact office@encyclopedia.pub.

OK

Confirm

Only members of the Encyclopedia advisory board for this topic are allowed to note entries. Would you like to become an advisory board member of the Encyclopedia?

Yes

No

${ textCharacter }/${ maxCharacter }

Submit

Cancel

Back

Comments

${ item }

|

More

No more~

There is no comment~

${ textCharacter }/${ maxCharacter }

Submit

Cancel

${ selectedItem.replyTextCharacter }/${ selectedItem.replyMaxCharacter }

Submit

Cancel

Confirm

Are you sure to Delete?

Yes

No