| Version | Summary | Created by | Modification | Content Size | Created at | Operation |

|---|---|---|---|---|---|---|

| 1 | Bigeng Chen | + 2949 word(s) | 2949 | 2022-02-18 11:14:32 | | | |

| 2 | Vicky Zhou | -9 word(s) | 2940 | 2022-03-01 03:08:13 | | |

Video Upload Options

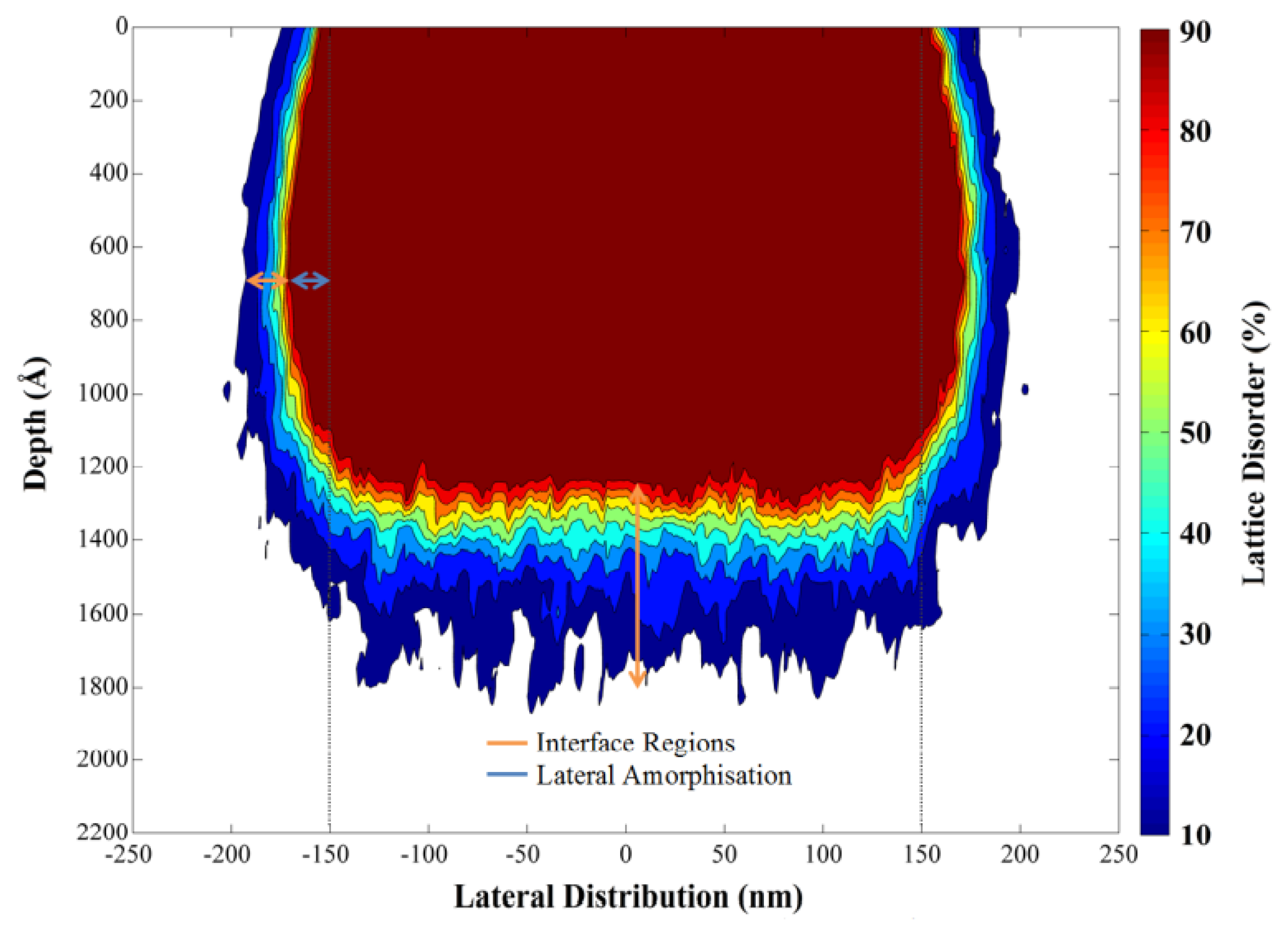

Germanium (Ge) ion implantation into silicon waveguides will induce lattice defects in the silicon, which can eventually change the crystal silicon into amorphous silicon and increase the refractive index from 3.48 to 3.96. A subsequent annealing process, either by using an external laser or integrated thermal heaters can partially or completely remove those lattice defects and gradually change the amorphous silicon back into the crystalline form and, therefore, reduce the material’s refractive index. In addition, Ge ion implantation and annealing are also demonstrated to enable post-fabrication trimming of ring resonators and Mach–Zehnder interferometers and to implement nonvolatile programmable photonic circuits.

1. Introduction

2. Ion Implantation and Annealing

2.1. Ge Ion Implantation

2.2. Annealing

3. Applications

3.1. Wafer-Scale Testing

3.2. Post-Fabrication Trimming of Optical Devices

3.3. Programmable Photonic Circuits

4. Conclusions

| Ref. [29] | Ref. [30] | Refs. [71][72] | Ref. [36] | |

|---|---|---|---|---|

| Methods | E-beam | UV light | Sb2Se3 | Ion implantation and annealing |

| CMOS compatibility of materials |

Yes | No | No | Yes |

| Throughput (minutes/device) | Low | Low | Low | High |

| (>17) | (>10) | (<1) | (<1) | |

| Effective index change | 0.06 | <0.1 | 0.017 | 0.19 |

References

- Richard, J.; Doussiere, P.; Driscoll, J.B.; Lin, W.; Yu, H.; Akulova, Y.; Komljenovic, T.; Bowers, J.E. Heterogeneously integrated InP/silicon photonics: Fabricating fully functional transceivers. IEEE Nanotechnol. Mag. 2019, 13, 17–26.

- Minkenberg, C.; Krishnaswamy, R.; Zilkie, A.; David, N. Co-packaged datacenter optics: Opportunities and challenges. IET Optoelectron. 2021, 15, 77–91.

- Westerveld, W.J.; Mahmud-Ul-Hasan, M.; Shnaiderman, R.; Ntziachristos, V.; Rottenberg, X.; Severi, S.; Rochus, V. Sensitive, small, broad-band and scalable optomechanical ultrasound sensor in silicon photonics. Nat. Photonics 2021, 15, 341–345.

- Baets, R. Silicon-Photonics-Based Spectroscopic Sensing for Environmental Monitoring and Health Care. In Proceedings of the Optical Fiber Communications Conference and Exhibition (OFC), San Francisco, CA, USA, 6–10 June 2021; pp. 1–42. Available online: https://www.photonics.intec.ugent.be/download/pub_4760.pdf (accessed on 8 February 2022).

- Chen, X.; Meng, F.; Fortune, S.A.; Compston, A.J.; Ebert, M.; Yan, X.; Du, H.; Banakar, M.; Tran, D.T.; Littlejohns, C.G.; et al. Silicon photonic beam steering module with backside coupling elements toward dense heterogeneous integration with drive electronics. APL Photonics 2021, 6, 116106.

- Shen, Y.; Harris, N.C.; Skirlo, S.; Prabhu, M.; Baehr-Jones, T.; Hochberg, M.; Sun, X.; Zhao, S.; Larochelle, H.; Englund, D.; et al. Deep learning with coherent nanophotonic circuits. Nat. Photonics 2017, 11, 441–446.

- Harris, N.C.; Carolan, J.; Bunandar, D.; Mihika, P.; Michael, H.; Baehr-Jones, T.; Michael, L.F.; Smith, A.M.; Tison, C.C.; Alsing, P.M.; et al. Linear programmable nanophotonic processors. Optica 2018, 5, 1623–1631.

- Apple is Entering Silicon Photonics. Available online: http://www.yole.fr/Silicon_Photonics_Market_Update_2021.aspx (accessed on 8 February 2022).

- Chen, X.; Milosevic, M.M.; Stanković, S.; Reynolds, S.; Bucio, T.D.; Li, K.; Thomson, D.J.; Gardes, F.; Reed, G.T. The emergence of silicon photonics as a flexible technology platform. Proc. IEEE 2018, 106, 2101–2116.

- Silicon Photonics Reaches Tipping Point, with Transceivers Shipping in Volume. Available online: http://www.semiconductor-today.com/features/PDF/semiconductor-today-april-may-2018-Silicon-photonics.pdf (accessed on 8 February 2022).

- Traverso, M.; Mazzini, M.; Lakshmikumar, K.; Sunder, S.; Kurylak, A.; Appel, C.; Muzio, C.; Tummidi, R.; Cervasio, A.; Nadeau, M.; et al. Integrated Silicon Photonics Transceiver Module for 100Gbit/s 20km Transmission. In Proceedings of the 2021 Optical Fiber Communications Conference and Exhibition (OFC), San Francisco, CA, USA, 6–10 June 2021; pp. 1–3. Available online: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9489560 (accessed on 8 February 2022).

- Jaturaphagorn, P.; Chattham, N.; Limsuwan, P.; Chaisakul, P. Optimization of end-fire coupling between an LED mid-IR light source and SiNx optical waveguides for spectroscopic sensing. Results Opt. 2021, 5, 100174.

- Han, Y.-T.; Yun, S.-J.; Jung, H.-D.; Kim, S.-T.; Shin, J.-U.; Park, S.-H.; Lee, S.-Y.; Baek, Y. A hybrid-integrated 400G TROSA module using chip-to-chip optical butt-coupling. In Proceedings of the Optical Fiber Communication Conference, San Diego, CA, USA, 8–12 March 2020; Optical Society of America: Washington, DC, USA, 2020; p. 1.

- Zhang, W.-Q.; Gao, M.-X.; Guo, B. Tunable modulation of photonic spin Hall effect by using a prism-coupling waveguide with hyperbolic metamaterials. JOSA B 2020, 37, 3777–3783.

- Selvaraja, S.K.; Vermeulen, D.; Schaekers, M.; Sleeckx, E.; Bogaerts, W.; Roelkens, G.; Dumon, P.; Thourhout, D.V.; Baets, R. Highly efficient grating coupler between optical fiber and silicon photonic circuit. In Proceedings of the Conference on Lasers and Electro-Optics and 2009 Conference on Quantum electronics and Laser Science Conference, Baltimore, MD, USA, 2–4 June 2009; pp. 1–2.

- Verenbergh, V.T.; Sun, P.; Hooten, S.; Jain, M.; Wilmart, Q.; Seyedi, A.; Huang, Z.; Fiorentino, M.; Beausoleil, R. Wafer-level testing of inverse-designed and adjoint-inspired vertical grating coupler designs compatible with DUV lithography. Opt. Express 2021, 29, 37021–37036.

- Cheng, L.; Mao, S.; Li, Z.; Han, Y.; Fu, H.Y. Grating couplers on silicon photonics: Design principles, emerging trends and practical issues. Micromachines 2020, 11, 666.

- Topley, R.; Martinez-Jimenez, G.; O’Faolain, L.; Healy, H.; Mailis, S.; Thomson, D.J.; Gardes, F.Y.; Peacock, A.C.; Payne, D.; Mashanovich, G.Z.; et al. Locally erasable couplers for optical device testing in silicon on insulator. J. Lightwave Technol. 2014, 32, 2248–2253.

- Yu, X.; Chen, X.; Milosevic, M.M.; Yan, X.; Saito, S.; Reed, G.T. Electrically Erasable Optical I/O for Wafer Scale Testing of Silicon Photonic Integrated Circuits. IEEE Photonics J. 2020, 12, 1–8.

- Liu, J.; Huang, G.; Wang, R.N.; He, J.; Raja, A.S.; Liu, T.; Engelsen, N.J.; Kippenberg, T.J. High-yield, wafer-scale fabrication of ultralow-loss, dispersion-engineered silicon nitride photonic circuits. Nat. Commun. 2021, 12, 1–9.

- Park, J.-W.; Sim, E.-D.; Beak, Y.-S. Improvement of fabrication yield and loss uniformity of waveguide mirror. IEEE Photonics Technol. Lett. 2005, 17, 807–809.

- Weinstein, D.; Bhave, S.A.; Tada, M.; Mitarai, S.; Morita, S.; Ikeda, K. Mechanical coupling of 2D resonator arrays for MEMS filter applications. In Proceedings of the IEEE International Frequency Control Symposium Joint with the 21st European Frequency and Time Forum, Geneva, Switzerland, 29 May–1 June 2007; IEEE: Piscataway, NJ, USA, 2007; pp. 1362–1365.

- Horikawa, T.; Shimura, D.; Jeong, S.-H.; Tokushima, M.; Kinoshita, K.; Mogami, T. The impacts of fabrication error in Si wire-waveguides on spectral variation of coupled resonator optical waveguides. Microelectron. Eng. 2016, 156, 46–49.

- Lee, T.; Lee, D.; Chung, Y. Design and simulation of fabrication-error-tolerant triplexer based on cascaded Mach–Zehnder inteferometers. IEEE Photonics Technol. Lett. 2007, 20, 33–35.

- Yen, T.-H.; Hung, Y.J. Fabrication-tolerant CWDM (de) multiplexer based on cascaded Mach-Zehnder interferometers on silicon-on-insulator. J. Lightwave Technol. 2020, 39, 146–153.

- Jayatilleka, H.; Frish, H.; Kumar, R.; Heck, J.; Ma, C.; Sakib, M.N.; Huang, D.; Rong, H. Post-Fabrication Trimming of Silicon Photonic Ring Resonators at Wafer-Scale. J. Lightwave Technol. 2021, 39, 5083–5088.

- Lushchik, A.; Kuzovkov, V.N.; Kotomin, E.A.; Prieditis, G.; Seeman, V.; Shablonin, E.; Vasil’chenko, E.; Popov, A.I. Evidence for the formation of two types of oxygen interstitials in neutron-irradiated α-Al2O3 single crystals. Sci. Rep. 2021, 11, 1–10.

- Schrauwen, J.; Van, T.D.; Baets, R. Trimming of silicon ring resonator by electron beam induced compaction and strain. Opt. Express 2008, 16, 3738–3743.

- Prorok, S.; Petrov, A.Y.; Eich, M.; Luo, J.; Jen, A. Trimming of high-Q-factor silicon ring resonators by electron beam bleaching. Opt. Lett. 2012, 37, 3114–3116.

- Zhou, L.; Okamoto, K.; Yoo, S.J.B. Athermalizing and trimming of slotted silicon microring resonators with UV-sensitive PMMA upper-cladding. IEEE Photonics Technol. Lett. 2009, 21, 1175–1177.

- Canciamilla, A.; Grillanda, S.; Morichetti, F.; Ferrari, C.; Hu, L.; Musgraves, J.D.; Richardson, K.; Agarwal, A.; Kimerling, L.C.; Melloni, A. Photo-induced trimming of coupled ring-resonator filters and delay lines in As2S3 chalcogenide glass. Opt. Lett. 2011, 36, 4002–4004.

- Atabaki, A.H.; Eftekhar, A.A.; Askari, M.; Adibi, A. Accurate post-fabrication trimming of ultra-compact resonators on silicon. Opt. Express 2013, 21, 14139–14145.

- Bachman, D.; Chen, Z.; Fedosejevs, R.; Tsui, Y.Y.; Van, V. Permanent fine tuning of silicon microring devices by femtosecond laser surface amorphization and ablation. Opt. Express 2013, 21, 11048–11056.

- Chen, X.; Milosevic, M.M.; Thomson, D.J.; Khokhar, A.Z.; Franz, Y.; Runge, A.; Mailis, S.; Peacock, A.C.; Reed, G.T. Post-fabrication phase trimming of Mach-Zehnder interferometers by laser annealing of germanium im-planted waveguides. Photonics Res. 2017, 5, 578–582.

- Milosevic, M.M.; Chen, X.; Cao, W.; Runge, A.; Franz, Y.; Littlejohns, C.G.; Mailis, S.; Peacock, A.C.; Thomson, D.J.; Reed, G.T. Ion implantation in silicon for trimming the operating wavelength of ring resonators. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–7.

- Milosevic, M.M.; Chen, X.; Yu, X.; Dinsdale, N.J.; Aktas, O.; Oo, S.Z.; Khokhar, A.Z.; Thomson, D.J.; Muskens, O.L.; Chong, H.M.H.; et al. Ion implantation of germanium into silicon for critical coupling control of racetrack resonators. J. Lightwave Technol. 2020, 38, 1865–1873.

- Chen, B.; Yu, X.; Chen, X.; Milosevic, M.M.; Thomson, D.J.; Khokhar, A.Z.; Saito, S.; Muskens, O.L.; Reed, G.T. Real-time monitoring and gradient feedback enable accurate trimming of ion-implanted silicon photonic devices. Opt. Express 2018, 26, 24953–24963.

- Chen, X.; Milosevic, M.M.; Runge, A.F.J.; Yu, X.; Khokhar, A.Z.; Mailis, S.; Thomson, D.J.; Peacock, A.C.; Saito, S.; Reed, G.T. Silicon erasable waveguides and directional couplers by germanium ion implantation for configurable photonic circuits. Opt. Express 2020, 28, 17630–17642.

- Pérez-López, D.; López, A.; DasMahapatra, P.; Capmany, J. Multipurpose self-configuration of programmable photonic circuits. Nat. Commun. 2020, 11, 1–11.

- Kotomin, E.; Kuzovkov, V.; Popov, A.I.; Maier, J.; Vila, R. Anomalous kinetics of diffusion-controlled defect annealing in irradiated ionic solids. J. Phys. Chem. A 2018, 122, 28–32.

- Baranova, E.C.; Gusev, V.M.; Martynenko, Y.V.; Starinin, C.V.; Hailbullin, I.B. On silicon amorphisation during different mass ions implantation. Rediation Eff. 1973, 18, 21–26.

- Townsend, P.D.; Chandler, P.J.; Zhang, L. Optical Effects of Ion Implantation; Cambridge University Press: Cambridge, UK, 1994.

- Heidemann, K.F. Complex-refractive-index profiles of 4 MeV Ge ion-irradiation damage in silicon. Philos. Mag. B 1981, 44, 465–485.

- Picraux, S.T.; Westmoreland, J.E.; Mayer, J.W.; Hart, R.R.; Marsh, O.J. Temperature dependence of lattice disorder created in Si by 40 keV Sb ions. Appl. Phys. Lett. 1969, 14, 7–9.

- Topley, R.; O’Faolain, L.; Thomson, D.J.; Gardes, F.Y.; Mashanovich, G.Z.; Reed, G.T. Planar surface implanted diffractive grating couplers in SOI. Opt. Express 2014, 22, 1077–1084.

- Lulli, G.; Bianconi, M.; Parisini, A.; Napolitani, E. Structural characterization and modeling of damage accumulation in In implanted Si. J. Appl. Phys. 2004, 95, 150–155.

- Albertazzi, E.; Bianconi, M.; Lulli, G.; Nipoti, R.; Carnera, A.; Cellini, C. Dynamic Monte Carlo simulation of nonlinear damage growth during ion implantation of crystalline silicon. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 1996, 112, 152–155.

- Lulli, G.; Albertazzi, E. King Software; CNR-IMM Bologna, via Gobetti 101, 40129 Bologna. 2007. Available online: https://publications.cnr.it/doc/186001 (accessed on 8 February 2022).

- Kang, H. Crystalline Silicon vs. Amorphous Silicon: The Significance of Structural Differences in Photovoltaic Applications. IOP Conf. Ser. Earth Environ. Sci. 2021, 726, 012001.

- Topley, R. Erasable Diffractive Grating Couplers in Silicon on Insulator. Doctoral Thesis, University of Southampton, Southampton, UK, 2014. Available online: https://eprints.soton.ac.uk/371751/ (accessed on 8 February 2022).

- Heidemann, K.F. The propagation of light waves through oxygen irradiation induced depth profiles of the complex refractive index in silicon. Phys. Status Solidi A 1981, 68, 607–617.

- Lee, B.H.; Kang, L.; Nieh, R.; Qi, W.J.; Lee, J.C. Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. Appl. Phys. Lett. 2000, 76, 1926–1928.

- Bell, A.E. Review and analysis of laser annealing. Rca Rev. 1979, 40, 295.

- Phillips, K.C.; Gandhi, H.H.; Mazur, E.; Sundaram, S.K. Ultrafast laser processing of materials: A review. Adv. Opt. Photonics 2015, 7, 684–712.

- Sharma, J.; Li, H.; Xuan, Z.; Kumar, R.; Hsu, C.M.; Sakib, M.; Liao, P.; Rong, H.; Jaussi, J.; Balamurugan, G. Silicon Photonic Micro-Ring Modulator-based 4 × 112 Gb/s O-band WDM Transmitter with Ring Photocurrent-based Thermal Control in 28 nm CMOS. In Proceedings of the 2021 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–2.

- Kumar, V.; Maan, A.S.; Akhtar, J. Defect levels in high energy heavy ion implanted 4H-SiC. Mater. Lett. 2022, 308, 131150.

- Kumar, V.; Maan, A.S.; Akhtar, J. Selective SHI irradiation for mesa type edge termination in semiconductor planar junction. J. Phys. Conf. Ser. 2013, 423, 012057.

- Sourani, F.; Enayati, M.H.; Ashrafizadeh, F.; Sayyedan, F.S.; Chu, P.K. Enhancing surface properties of (Fe, Cr) Al-Al2O3 nanocomposite by oxygen ion implantation. J. Alloy. Compd. 2021, 853, 156892.

- Xu, F.; Tan, Y.; Xie, Z.; Zhang, B. Implantation energy-and size-dependent light output of enhanced-efficiency micro-LED arrays fabricated by ion implantation. Opt. Express 2021, 29, 7757–7766.

- Pazniak, H.; Benchakar, M.; Bilyk, T.; Liedl, A.; Busby, Y.; Noël, C.; Chartier, P.; Hurand, S.; Marteau, M.; Houssiau, L.; et al. Ion Implantation as an Approach for Structural Modifications and Functionalization of Ti3C2Tx MXenes. ACS Nano 2021, 15, 4245–4255.

- Yan, C.; Zeng, Q.; He, W.; Zhu, J. Enhanced surface hardness and tribocorrosion performance of 60NiTi by boron ion implantation and post-annealing. Tribol. Int. 2021, 155, 106816.

- Castaldini, A.; Cavallini, A.; Rigutti, L.; Nava, F. Low temperature annealing of electron irradiation induced defects in 4H-SiC. Appl. Phys. Lett. 2004, 85, 3780–3782.

- Wu, J.; He, Z.; Guo, Z.; Tian, R.; Wang, F.; Liu, M.; Yang, X.; Fan, Z.; Yang, F. Pulsed Laser Annealing of Phosphorous-Implanted 4H-SiC: Electrical and Structural Characteristics. J. Electron. Mater. 2022, 51, 172–178.

- Roccaforte, F.; Giannazzo, F.; Greco, G. Ion Implantation Doping in Silicon Carbide and Gallium Nitride Electronic Devices. Micro 2022, 2, 23–53.

- Shoji, Y.; Kintaka, K.; Suda, S.; Kawashima, H.; Hasama, T.; Ishikawa, H. Low-crosstalk 2 × 2 thermo-optic switch with silicon wire waveguides. Opt. Express 2010, 18, 9071–9075.

- Miller, D.A.B. Self-aligning universal beam coupler. Opt. Express 2013, 21, 6360–6370.

- Ríos, C.; Stegmaier, M.; Hosseini, P.; Wang, D.; Scherer, T.; Wright, C.D.; Bhaskaran, H.; Pernice, W.H. Integrated all-photonic non-volatile multi-level memory. Nat. Photonics 2015, 9, 725–732.

- Wuttig, M.; Bhaskaran, H.; Taubner, T. Phase-change materials for non-volatile photonic applications. Nat. Photonics 2017, 11, 465–476.

- Errando-Herranz, C.; Takabayashi, A.Y.; Edinger, P.; Sattari, H.; Gylfason, K.B.; Quack, N. MEMS for photonic integrated circuits. IEEE J. Sel. Top. Quantum Electron. 2019, 26, 1–16.

- Quack, N.; Sattari, H.; Takabayashi, A.Y.; Zhang, Y.; Verheyen, P.; Bogaerts, W.; Edinger, P.; Errando-Herranz, C.; Gylfason, K.B. MEMS-enabled silicon photonic integrated devices and circuits. IEEE J. Quantum Electron. 2019, 56, 1–10.

- Ríos, C.; Du, Q.; Zhang, Y.; Popescu, C.C.; Shalaginov, M.Y.; Miller, P.; Roberts, C.; Kang, M.; Richardson, K.A.; Gu, T.; et al. Ultra-compact nonvolatile photonics based on electrically reprogrammable transparent phase change materials. arXiv 2021, arXiv:2105.06010.

- Delaney, M.; Zeimpekis, I.; Du, H.; Yan, X.; Banakar, M.; Thomson, D.J.; Hewak, D.W.; Muskens, O.L. Nonvolatile programmable silicon photonics using an ultralow-loss Sb2Se3 phase change material. Sci. Adv. 2021, 7, 3500.