| Version | Summary | Created by | Modification | Content Size | Created at | Operation |

|---|---|---|---|---|---|---|

| 1 | Filippo Giannazzo | + 2441 word(s) | 2441 | 2021-11-30 06:42:31 | | | |

| 2 | Dean Liu | Meta information modification | 2441 | 2021-12-15 02:23:03 | | |

Video Upload Options

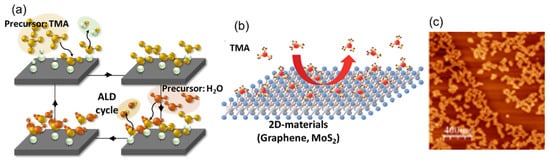

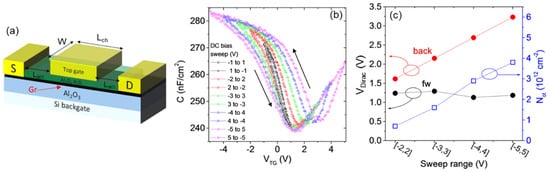

Atomic layer deposition (ALD) of high-κ dielectrics on two-dimensional (2D) materials (including graphene and transition metal dichalcogenides) still represents a challenge due to the lack of out-of-plane bonds on the pristine surfaces of 2D materials, thus making the nucleation process highly disadvantaged. The typical methods to promote the nucleation (i.e., the predeposition of seed layers or the surface activation via chemical treatments) certainly improve the ALD growth but can affect, to some extent, the electronic properties of 2D materials and the interface with high-κ dielectrics. Hence, direct ALD on 2D materials without seed and functionalization layers remains highly desirable. In this context, a crucial role can be played by the interaction with the substrate supporting the 2D membrane. In particular, metallic substrates such as copper or gold have been found to enhance the ALD nucleation of Al2O3 and HfO2 both on monolayer (1 L) graphene and MoS2. Similarly, uniform ALD growth of Al2O3 on the surface of 1 L epitaxial graphene (EG) on SiC (0001) has been ascribed to the peculiar EG/SiC interface properties.

1. Introduction

2. Atomic Layer Deposition on 2D Materials

2.1. Methods to Promote ALD Growth on 2D Materials

| Ref | 2D Material | ALD Process | ||||

|---|---|---|---|---|---|---|

| ALD Activation | TALD (°C) | High-κ Type | Uniformity | 2D Damage | ||

| Seed layer deposition | ||||||

| [24] | CVD-graphene on SiO2 | 3,4,9,10-perylene tetracarboxylic acid (PTCA) | 100 °C | Al2O3, ~2 nm | High | Not |

| [25] | CVD-graphene on SiO2 | Poly(4-vinylphenol) (PVP) | ------ | Al2O3, 20 nm | High | Not |

| [26] | CVD-MoS2 and CVD-WS2 | Perylene bisimide | 80 °C | Al2O3, ~3 nm | High | Not |

| [27] | Exfoliated graphene | Evaporated Al | 250 °C | Al2O3, ~3 nm | High for seed layer > 1.2 nm | Not |

| [28][29] | CVD-MoS2 | Al | 150 °C | ZrO2, ~15 nm | High | Not |

| [30] | MoS2 by sulfurization of Mo | SiO2 nanoparticles | 300 °C | Al2O3, 5.7 nm HfO2, 2.8 nm |

High | Not |

| [31] | Exfoliated graphene | Seed layer of H2O-assisted dielectric at low temperature (100 °C) | 100 °C | Al2O3, ~11 nm | High | Not |

| [32] | Transferred CVD-graphene on SiO2 | Seed layer of H2O-assisted dielectric at low temperature (100 °C) | 250 °C | Al2O3, ~22 nm | High | Not |

| [33] | Exfoliated MoS2 | Seed layer of H2O-assisted dielectric at low temperature (80 °C) | 180°C | Al2O3, <10 nm | High | Not |

| [34] | Exfoliated WS2 | Evaporated Al | 95 °C | HfO2, ~20 nm | High | Not |

| Chemical functionalization |

||||||

| [35] | Exfoliated graphene | NO2 | 250 °C | Al2O3, ~12 nm | High | Current and mobility degradation |

| [36] | Exfoliated graphene | O3 (25–200 °C) | 200 °C | Al2O3, ~15 nm | High | Significant defect amount during O3 treatment at 200 °C |

| [23] | Exfoliated MoS2 | O3 (30°) | 200 °C | Al2O3, ~5 nm | High | Not |

| [37][38] | HOPG | O3 (25°) | 200 °C | Al2O3, ~10 nm | High | Damage to 2D crystal |

| [39] | Exfoliated MoSe2, WSe2 | UV-O3 | 200 °C | HfO2, ~4 nm | High on MoSe2 Low on WSe2 |

Partial etching of the 2D layers |

| [40] | Exfoliated MoS2 | O2-plasma | 250 °C | Al2O3, ~10 nm HfO2, ~10 nm |

High | MoS2 oxidation |

| [41] | Transferred CVD-graphene | O2-plasma | 100 °C | Al2O3, ~10 nm | High | Significant amount of defects |

| [42] | Exfoliated graphene | N2-plasma | ------ | Al2O3, ~28 nm | High | Significant amount of defects and reduced conductivity |

| ALD parameter tuning |

||||||

| [43] | Exfoliated graphene | Low-temperature ALD process | 80–150 °C | Al2O3 | High (98%) at 80 °C | Not |

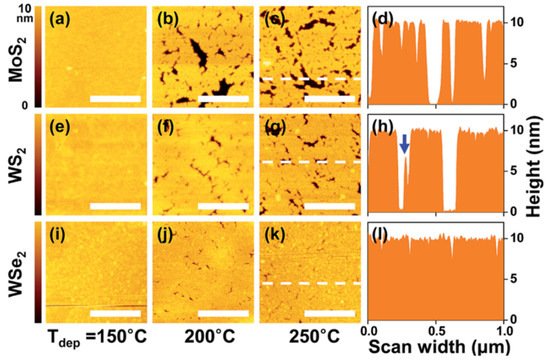

| [22] | Exfoliated MoS2, WS2, WSe2, h-BN | Low-temperature ALD process | 150 °C | Al2O3, 1, 10 nm | Variable as the 2D polarizability (WSe2 < WS2 < MoS2 < h-BN) | Not |

| [44] | Exfoliated HOPG and MoS2 | Low-temperature ALD process | 50 °C | Al2O3, few nm | High | Not |

| [43] | CVD graphene on Cu | Long or multiple precursor pulses | 200 °C | Al2O3, few nm | Variable | Not |

- (i)

-

Predeposition of a seed-layer;

- (ii)

-

Chemical pre-functionalization.

2.2. Electrical Behavior and Interface Quality of High-κ Dielectrics by ALD on 2D Materials

References

- Du, X.; Skachko, I.; Barker, A.; Aandrei, E.Y. Approaching ballistic transport in suspended graphene. Nat. Nanotechnol. 2008, 3, 491.

- Giannazzo, F.; Sonde, S.; Lo Nigro, R.; Rimini, E.; Raineri, V. Mapping the Density of Scattering Centers Limiting the Electron Mean Free Path in Graphene. Nano Lett. 2011, 11, 4612–4618.

- Lin, Y.-M.; Dimitrakopoulos, C.; Jenkins, K.A.; Farmer, D.B.; Chiu, H.-Y.; Grill, A.; Avouris, P. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. Science 2010, 327, 662.

- Moon, J.S.; Curtis, D.; Hu, M.; Wong, D.; McGuire, C.; Campbell, P.M.; Jernigan, G.; Tedesco, J.L.; VanMil, B.; Myers-Ward, R.; et al. Epitaxial-Graphene RF Field-Effect Transistors on Si-Face 6H-SiC Substrates. IEEE Electron Device Lett. 2009, 30, 650–652.

- Liu, H.; Neal, A.T.; Ye, P.D. Channel Length Scaling of MoS2 MOSFETs. ACS Nano 2012, 6, 8563–8569.

- Liu, Y.; Guo, J.; Wu, Y.; Zhu, E.; Weiss, N.O.; He, Q.; Wu, H.; Cheng, H.-C.; Xu, Y.; Shakir, I.; et al. Pushing the Performance Limit of Sub-100 nm Molybdenum Disulfide Transistors. Nano Lett. 2016, 16, 6337–6342.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150.

- Kim, S.; Konar, A.; Hwang, W.S.; Lee, J.H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J.B.; Choi, J.Y.; et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals. Nat. Commun. 2012, 3, 1011.

- Mak, K.F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T.F. Atomically Thin MoS2: A New Direct-Gap Semiconductor. Phys. Rev. Lett. 2010, 105, 136805.

- Splendiani, A.; Sun, L.; Zhang, Y.; Li, T.; Kim, J.; Chim, C.-Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer MoS2. Nano Lett. 2010, 10, 1271–1275.

- Reddy, D.; Register, L.F.; Carpenter, G.D.; Banerjee, S.K. Graphene Field-Effect Transistors. J. Phys. D Appl. Phys. 2011, 45, 019501.

- Echtermeyer, T.J.; Lemme, M.C.; Baus, M.; Szafranek, B.N.; Geim, A.K.; Kurz, H. Non-volatile switching in graphene field effect devices. IEEE Electron Device Lett. 2008, 29, 29952–29954.

- Fisichella, G.; Lo Verso, S.; Di Marco, S.; Vinciguerra, V.; Schilirò, E.; Di Franco, S.; Lo Nigro, R.; Roccaforte, F.; Zurutuza, A.; Centeno, A.; et al. Advances in the fabrication of graphene transistors on flexible substrates. Beilstein J. Nanotechnol. 2017, 8, 467–474.

- Liu, H.; Ye, P.D. MoS2 Dual-Gate MOSFET With Atomic-Layer-Deposited Al2O3 as Top-Gate Dielectric. IEEE Electron Device Lett. 2011, 33, 546–548.

- Giannazzo, F.; Greco, G.; Roccaforte, F.; Sonde, S.S. Vertical Transistors Based on 2D Materials: Status and Prospects. Crystals 2018, 8, 70.

- Giannazzo, F. Engineering 2D heterojunctions with dielectrics. Nat. Electron. 2019, 2, 54.

- Giannazzo, F.; Fisichella, G.; Greco, G.; Schilirò, E.; Deretzis, I.; Lo Nigro, R.; La Magna, A.; Roccaforte, F.; Iucolano, F.; Lo Verso, S.; et al. Cordier, Fabrication and Characterization of Graphene Heterostructures with Nitride semiconductors for High Frequency Vertical Transistors. Phys. Status Solidi 2017, 215, 1700653.

- Giannazzo, F.; Greco, G.; Schilirò, E.; Lo Nigro, R.; Deretzis, I.; La Magna, A.; Roccaforte, F.; Iucolano, F.; Ravesi, S.; Frayssinet, E.; et al. High-performance graphene/AlGaN/GaN schottky junctions for hot electron transistors. ACS Appl. Electron. Mater. 2019, 1, 2342–2354.

- Mehr, W.; Dabrowski, J.; Scheytt, J.C.; Lippert, G.; Xie, Y.H.; Lemme, M.C.; Ostling, M.; Lupina, G. Vertical Graphene Base Transistor. IEEE Electron Device Lett. 2012, 33, 691–693.

- Bae, T.-E.; Kim, H.; Jung, J.; Cho, W.-J. Fabrication of high-performance graphene field-effect transistor with solution-processed Al2O3 sensing membrane. Appl. Phys. Lett. 2014, 104, 153506.

- Oviroh, P.O.; Akbarzadeh, R.; Pan, D.; Coetzee, R.A.M.; Jen, T.-C. New development of atomic layer deposition: Processes, methods and applications. Sci. Technol. Adv. Mater. 2019, 20, 465–496.

- Park, T.; Kim, H.; Leem, M.; Ahn, W.; Choi, S.; Kim, J.; Uh, J.; Kwon, K.; Jeong, S.-J.; Park, S.; et al. Atomic layer deposition of Al2O3 on MoS2, WS2, WSe2, and h-BN: Surface coverage and adsorption energy. RSC Adv. 2017, 7, 884–889.

- Cheng, L.; Qin, X.; Lucero, A.T.; Azcatl, A.; Huang, J.; Wallace, R.M.; Cho, K.; Kim, J. Atomic Layer Deposition of a High-k Dielectric on MoS2 Using Trimethylaluminum and Ozone. ACS Appl. Mater. Interfaces 2014, 6, 11834–11838.

- Wang, X.; Tabakman, S.M.; Dai, H. Atomic Layer Deposition of Metal Oxides on Pristine and Functionalized Graphene. J. Am. Chem. Soc. 2008, 130, 8152.

- Shin, W.C.; Kim, T.Y.; Sul, O.; Cho, B.J. Seeding atomic layer deposition of high-k dielectric on graphene with ultrathin poly(4-vinylphenol) layer for enhanced device performance and reliability. Appl. Phys. Lett. 2012, 101, 033507.

- Wirtz, C.; Hallam, T.; Cullen, C.P.; Berner, N.C.; O’Brien, M.; Marcia, M.; Hirsch, A.; Duesberg, G.S. Atomic layer deposition on 2D transition metal chalcogenides: Layer dependent reactivity and seeding with organic ad-layers. Chem. Commun. 2015, 51, 16553.

- Fallahazad, B.; Lee, K.; Lian, G.; Kim, S.; Corbet, C.; Ferrer, D.; Colombo, L.; Tutuc, E. Scaling of Al2O3 dielectric for graphene field-effect transistors. Appl. Phys. Lett. 2012, 100, 093112.

- Guo, T.; Wu, H.; Su, X.; Guo, B.; Liu, C. Surface functionalization toward top-gated monolayer MoS2 field-effect transistors with ZrO2/Al2O3 as composite dielectrics. J. Alloy. Compd. 2021, 871, 159116.

- Woo, W.J.; Oh, I.K.; Park, B.E.; Kim, Y.; Park, J.; Seo, S.; Song, J.-G.; Jung, H.; Kim, D.; Lim, J.H.; et al. Bi-layer high-k dielectrics of Al2O3/ZrO2 to reduce damage to MoS2 channel layers during atomic layer deposition. 2D Mater. 2019, 6, 015019.

- Haodong, Z.; Arutchelvan, G.; Meersschaut, J.; Gaur, A.; Conard, T.; Bender, H.; Lin, D.; Asselberghs, I.; Heyns, M.; Radu, I.; et al. MoS2 Functionalization with a Sub-nm Thin SiO2 Layer for Atomic Layer Deposition of High-κ Dielectrics. Chem. Mater. 2017, 29, 6772–6780.

- Zhang, Y.; Qiu, Z.; Cheng, X.; Xie, H.; Wang, H.; Xie, X.; Yu, Y.; Liu, R. Direct growth of high-quality Al2O3 dielectric on graphene layers by low-temperature H2O-based ALD. J. Phys. D Appl. Phys. 2014, 47, 055106.

- Fisichella, G.; Schilirò, E.; Di Franco, S.; Fiorenza, P.; Lo Nigro, R.; Roccaforte, F.; Ravesi, S.; Giannazzo, F. Interface Electrical Properties of Al2O3 Thin Films on Graphene Obtained by Atomic Layer Deposition with an in Situ Seedlike Layer. ACS Appl. Mater. Interfaces 2017, 9, 7761–7771.

- Lin, Y.-S.; Cheng, P.-H.; Huang, K.-W.; Lin, H.-C.; Chen, M.-J. Atomic layer deposition of sub-10 nm high-K gate dielectrics on top-gated MoS2 transistors without surface functionalization. Appl. Surf. Sci. 2018, 443, 421–428.

- Gong, F.; Luo, W.; Wang, J.; Wang, P.; Fang, H.; Zheng, D.; Guo, N.; Wang, J.; Luo, M.; Ho, J.C.; et al. High-Sensitivity Floating-Gate Phototransistors Based on WS2 and MoS2. Adv. Funct. Mater. 2016, 26, 6084–6090.

- Lin, Y.M.; Jenkins, K.A.; Valdes-Garcia, A.; Small, J.P.; Farmer, D.B.; Avouris, P. Operation of Graphene Transistors at Gigahertz Frequencies. Nano Lett. 2009, 9, 422.

- Lee, B.; Mordi, G.; Kim, M.J.; Chabal, Y.J.; Vogel, E.M.; Wallace, R.M.; Cho, K.J.; Colombo, L.; Kim, J. Characteristics of high-k Al2O3 dielectric using ozone-based atomic layer deposition for dual-gated graphene devices. J. Appl. Phys. Lett. 2010, 97, 043107.

- Lee, J.; Lee, B.; Kim, J.; Cho, K. Ozone Adsorption on Graphene: Ab Initio Study and Experimental Validation. J. Phys. Chem. C 2009, 113, 14225.

- Lee, B.; Park, S.Y.; Kim, H.C.; Cho, K.; Vogel, E.M.; Kim, M.J.; Wallace, R.M.; Kim, J. Conformal Al2O3 dielectric layer deposited by atomic layer deposition for graphene-based nanoelectronics. J. Appl. Phys. Lett. 2008, 92, 203102.

- Azcatl, A.; Santosh, K.C.; Peng, X.; Lu, N.; McDonnell, S.; Qin, X.; de Dios, F.; Addou, R.; Kim, J.; Kim, M.J.; et al. HfO2 on UV-O3 Exposed Transition Metal Dichalcogenides: Interfacial Reactions Study. 2D Mater. 2015, 2, 014004.

- Yang, J.; Kim, S.; Choi, W.; Park, S.H.; Jung, Y.; Cho, M.-H.; Kim, H. Improved Growth Behavior of Atomic-Layer-Deposited High-k Dielectrics on Multilayer MoS2 by Oxygen Plasma Pretreatment. ACS Appl. Mater. Interfaces 2013, 5, 4739–4744.

- Nayfeh, O.M.; Marr, T.; Dubey, M. Impact of Plasma-Assisted Atomic-Layer-Deposited Gate Dielectric on Graphene Transistors. IEEE Electron Device Lett. 2011, 32, 473–475.

- Lim, T.; Kim, D.; Ju, S. Direct deposition of aluminum oxide gate dielectric on graphene channel using nitrogen plasma treatment. Appl. Phys. Lett. 2013, 113, 013107.

- Aria, A.I.; Nakanishi, K.; Xiao, L.; Braeuninger-Weimer, P.; Sagade, A.A.; Alexander-Webber, J.A.; Hofmann, S. Parameter Space of Atomic Layer Deposition of Ultrathin Oxides on Graphene. ACS Appl. Mater. Interfaces 2016, 8, 30564.

- Kwak, I.; Kavrik, M.; Park, J.H.; Grissom, L.; Fruhberger, B.; Wong, K.T.; Kang, S.; Kummel, A.C. Low interface trap density in scaled bilayer gate oxides on 2D materials via nanofog low temperature atomic layer deposition. Appl. Surf. Sci. 2019, 463, 758–766.

- Kitzmann, J.; Göritz, A.; Fraschke, M.; Lukosius, M.; Wenger, C.; Wolff, A.; Lupina, G. Perfluorodecyltrichlorosilane-based seed-layer for improved chemical vapour deposition of ultrathin hafnium dioxide films on graphene. Sci. Rep. 2016, 6, 29223.

- Farmer, D.B.; Chiu, H.-Y.; Lin, Y.-M.; Jenkins, K.A.; Xia, F.; Avouris, P. Utilization of a Buffered Dielectric to Achieve High Field-Effect Carrier Mobility in Graphene Transistors. Nano Lett. 2009, 9, 4474.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S.K. Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric. Appl. Phys. Lett. 2009, 94, 062107.

- Iraiwa, A.; Matsumura, D.; Kawarada, H. Effect of atomic layer deposition temperature on current conduction in Al2O3 films formed using H2O oxidant. J. Appl. Phys. 2016, 120, 084504.

- Fallahazad, B.; Kim, S.; Colombo, L.; Tutuc, E. Dielectric Thickness Dependence of Carrier Mobility in Graphene with HfO2 Top Dielectric. Appl. Phys. Lett. 2010, 97, 123105.

- Zhao, P.; Khosravi, A.; Azcatl, A.; Bolshakov, P.; Mirabelli, G.; Caruso, E.; Hinkle, C.L.; Hurley, P.K.; Wallace, R.M.; Young, C.D. Evaluation of border traps and interface traps in HfO2/MoS2 gate stacks by capacitance–voltage analysis. 2D Mater. 2018, 5, 031002.

- Zhou, P.; Yang, S.; Sun, Q.; Chen, L.; Wang, P.; Ding, S.; Zhang, D.W. Direct Deposition of Uniform High-k Dielectrics on Graphene. Sci. Rep. 2014, 4, 6448.

- Dingemans, G.; van de Sanden, M.C.M.; Kessels, W.M.M. Influence of the Deposition Temperature on the c-Si Surface Passivation by Al2O3 Films Synthesized by ALD and PECVD. Electrochem. Solid-State Lett. 2010, 13, H76.