| Version | Summary | Created by | Modification | Content Size | Created at | Operation |

|---|---|---|---|---|---|---|

| 1 | Vivi Li | -- | 1029 | 2022-11-04 01:48:42 |

Video Upload Options

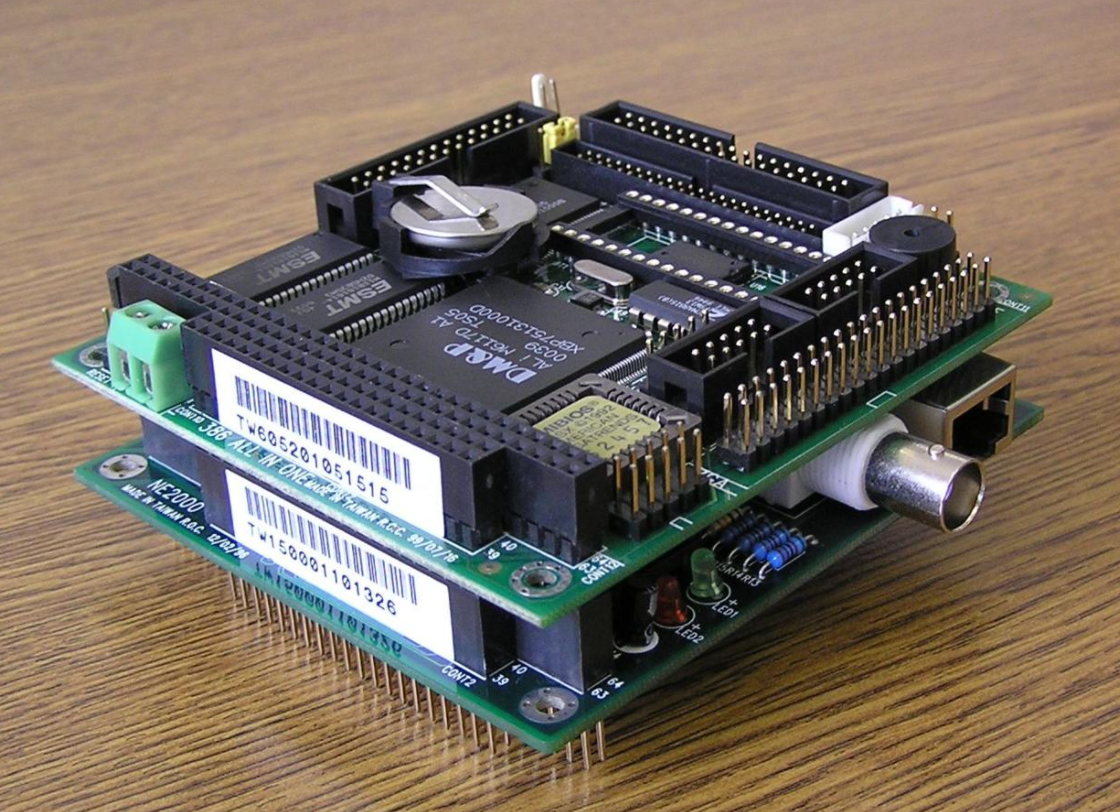

The Vortex86 is a computing system-on-a-chip (SoC) based on a core compatible with the x86 microprocessor family. It is produced by DM&P Electronics, but originated with Rise Technology.

1. History

Vortex86 previously belonged to SiS, which got the basic design from Rise Technology.[1] SiS sold it to DM&P Electronics[2] in Taiwan.

Before adopting the Vortex86 series, DM&P manufactured the M6117D, an Intel 386SX compatible, 25–40 MHz SoC.[3][4]

2. CPU

Vortex86 CPUs implement the IA-32 architecture but which instructions are implemented varies depending on the model. Vortex86SX[5] and the early versions of Vortex86 do not have a floating point unit (FPU). Any code that runs on i586 but does not use floating point instructions will run on these models. Any i586 code will run on Vortex86DX and later. Some Linux kernels (by build-time option) emulate the FPU on any CPU that is missing one, so a program that uses i586-level floating point instructions will work on any Vortex86 family CPU under such a kernel, albeit more slowly on a model with no FPU. The more advanced models have FPUs that have i686-level instructions, such as FUCOMI.

Code intended for i686 may fail on some models because they lack a Conditional Move (CMOV) instruction. Compilers asked to optimize code for a more advanced CPU (for example the GNU Compiler with its -march=i686 option) generate code that uses CMOV. Linux systems intended to run on i686 are generally not compatible with these Vortex86 models because the GNU C Library, when built for i686, uses a CMOV instruction in its assembly language strcmp function, which its dynamic loader (ld.so) uses. Hence, no program that uses shared libraries can execute.

Below are the properties of a Vortex86 original CPU reported by the Linux kernel tool /proc/cpuinfo.

Note that this CPU is a later version with an FPU.

processor : 0 vendor_id : SiS SiS SiS cpu family : 5 model : 0 model name : 05/00 stepping : 5 cpu MHz : 199.978 fdiv_bug : no hlt_bug : no f00f_bug : no coma_bug : no fpu : yes fpu_exception : yes cpuid level : 1 wp : yes flags : fpu tsc cx8 mmx up bogomips : 399.95 clflush size : 32 cache_alignment : 32 address sizes : 32 bits physical, 32 bits virtual power management:

3. Compatible Components

DM&P maintained an embedded Linux distribution customized to use the SoCs features.[6] Other operating systems may work depending on the SoC model, including various RTOS systems such as QNX and VxWorks, Linux distributions,[7] FreeBSD[8] or various versions of Microsoft Windows systems such as Windows Embedded Compact or Windows IoT.[9]

4. Versions

4.1. Vortex86 Original

This was developed by SiS and called SiS55x/Rise mP6 or simply Vortex86. It has three integer and MMX pipelines, branch prediction.[10]

4.2. Vortex86SX

This runs at 300 MHz and has 16 KB Data + 16 KB Instruction L1 cache, no FPU, no L2 cache. It can use both SD and DDR2 RAM.[11]

4.3. Vortex86DX

This runs at 600 MHz to 1 GHz (2.02 W @ 800 MHz [12]), and has 16 KB Data + 16 KB Instruction L1 cache, FPU, 256 KB L2 cache, 6-staged pipeline. It can address up to 1 GiB DDR2 RAM[13][14]

The PDX-600 is a version of the Vortex86DX that differs only in the number of RS-232 ports (3 instead of 5) and has no I²C and servo controllers, thus targeting more the embedded than the industrial market. Netbooks similar to the Belco 450R use this chip.[15]

The package is a single 581-pin BGA package.

4.4. Vortex86MX

This runs at 1 GHz. The CPU core hardly differs from the Vortex86DX, but according to several sources, the processor does appear to have implemented SIMD multi-media instructions (MMX).[16][17][18] This version drops conformance to ISA and integrates a GPU and a HD Audio controller, it also integrates a UDMA/100 IDE controller. The consumer grade version is known as the PMX-1000.[19] Current models of the Gecko Edubook use the Xcore86, a rebadge of the Vortex86MX.[19]

4.5. Vortex86MX+

This has a 32KB write through 2-way L1 cache, 256KB write through/write back 4-way L2 cache, PCI rev. 2.1 32-bit bus interface at 33 MHz, DDR2, ROM controller, IPC (Internal Peripheral Controllers with DMA and interrupt timer/counter included), Fast Ethernet, FIFO UART, USB2.0 Host and ATA controller. The MX+ Adds a VGA controller on chip with shared memory.

The package is a single 720-pin BGA package.

4.6. Vortex86DX2

This has a 32KB write through 4-way L1 cache (16K Instruction + 16K Data), 256KB write through/write back 4-way L2 cache, PCI rev. 2.1 32-bit bus interface at 33 MHz, DDR2, ROM controller, IPC (Internal Peripheral Controllers with DMA and interrupt timer/counter included), VGA, 100 Mbps ethernet, FIFO UART, USB2.0 Host and ATA controller. Enhancements over the DX include more COM ports (9), 2GB of RAM, and an HD Audio codec, as well as more GPIO pins.

The package is a single 720-pin BGA package.

4.7. Vortex86EX

This has a 32KB write through 2-way L1 cache, 128KB write through/write back 2-way L2 cache, PCI-e bus interface, 300 MHz DDR3, ROM controller, IPC (Internal Peripheral Controllers with DMA and interrupt timer/counter included), Fast Ethernet, FIFO UART, USB2.0 Host and ATA controller.

The package is a single 288-pin TFBGA-package.

4.8. Vortex86DX3

This has a 1.0 GHz dual-core i686-compatible CPU.[20][21] It has an eight-way 32K I-Cache, an eight-way 32K D-Cache, a four-way 512 KB L2 cache with a write-through or write-back policy, ability to use up to 2GB of DDR3 RAM, a PCI-e bus interface, 100 Mbps Ethernet, FIFO UART, a USB 2.0 host, integrated GPU, an ATA controller that has an IDE controller, PATA 100 (2x HDD) or 2x SD at Primary Channel, and SATA 1.5Gbit/s (1 Port) at Secondary Channel.

The package is a single 720-pin BGA-package.[22]

4.9. Vortex86EX2

The EX2 model has two asymmetrical master/slave CPU cores.[23] The master core runs at 600 MHz, has 16K I-Cache, 16K D-Cache, and four-way 128 KB L2 cache with a write-through or write-back policy. The slave core operates at 400 MHz and also has 16KB I-Cache, 16KB D-Cache, but has no L2 cache. Both have a built-in FPU. Maximum DDR3 RAM capacity is 2GB. It can also use ECC memory. It is produced using the 65 nm manufacturing process[24] and uses the 19x19 mm LFBGA-441 package.

References

- Cebit 2007: x86 Minisystem mit Vortex86SX (german) http://backup.orthy.de/index.php?option=com_content&view=article&id=4628:cebit-2007-x86-minisystem-mit-vortex86sx&catid=501:hardware&Itemid=56

- Vortex86 Envision Embedded Design with Windows Embedded Technologies (archived copy) https://web.archive.org/web/20060514054503/http://icop.contradata.it/site_images/PR_Vortex86%209-25-2002.pdf

- M6117D Data Sheet http://www.dmp.com.tw/app/webcamera/pdf/m6117d.pdf

- "M6117D overview". http://dmp.com.tw/tech/m6117d/.

- DM&P Vortex86SX FAQ http://www.dmp.com.tw/tech/vortex86sx/faq.htm

- X-Linux http://www.dmp.com.tw/tech/os-xlinux/

- Vortex86 Series Linux Support List http://www.vortex86.com/news/2

- VEX2-6427 Datasheet https://www.icop.com.tw/download?serial=VEX2-6427_datasheet

- Vortex86 Series Windows Support List http://www.vortex86.com/news/3

- Vortex86 Data Sheet http://download@ftp.dmp.com.tw/vortex86/doc/55x_ds09_0923.pdf

- Vortex86SX Data Sheet (archived copy) https://web.archive.org/web/20110706153051/http://www.indevices.com.br/downloads/V86SX-web-predatasheet.pdf

- Vortex86DX overview (archived copy) https://web.archive.org/web/20090426040951/http://www.vortex86dx.com/?page_id=80

- Vortex86DX documentation http://dmp.com.tw/tech/vortex86dx/

- Vortex86DX Data Sheet http://download@ftp.dmp.com.tw/vortex86dx/Vortex86DX_V0.9A_Brief.pdf

- engadget - "The world's cheapest laptop" https://www.engadget.com/2009/03/16/tnx-9500-the-worlds-cheapest-laptop-live-and-hands-on/

- Thomas, Alexander (November 2012). "BTplug Review". Dr. Lex' Site. http://dr-lex.be/hardware/btplug_review.html#perfo.

- Kauler, Barry (2010-01-16). "Xcore86 CPU in Gecko Edubook". Barry's Blog. http://bkhome.org/blog/?viewDetailed=01341. — See blog comments for more information.

- LoneRifle (2010-01-22). "CPU Features". Flickr. https://www.flickr.com/photos/46578721@N08/4296160520/.

- Angel, Jonathan (2008-12-11). "X86 system-on-chip adds VGA graphics". LinuxForDevices. http://www.linuxfordevices.com/c/a/News/X86-systemonchip-adds-VGA-graphics/.

- http://www.compactpc.com.tw/products/about OS support list

- Vortex86DX3 product overview http://www.vortex86.com/products/Vortex86DX3

- "Vortex86DX3 is a New x86 SoC for Embedded Systems - CNX Software". 9 April 2015. http://www.cnx-software.com/2015/04/09/vortex86dx3-is-a-new-x86-soc-for-embedded-systems/.

- Vortex86EX2 product overview http://www.vortex86.com/products/Vortex86EX2

- ICOP Vortex86 SoC website https://www.icop.com.tw/article/205