Your browser does not fully support modern features. Please upgrade for a smoother experience.

Please note this is an old version of this entry, which may differ significantly from the current revision.

Subjects:

Engineering, Electrical & Electronic

Gallium nitride (GaN) possesses remarkable characteristics such as a wide bandgap, high critical electric field, robust antiradiation properties, and a high saturation velocity for high-power devices. These attributes position GaN as a pivotal material for the development of power devices.

- GaN power device

- breakdown voltage

- specific on-resistance

1. Introduction

Power semiconductor devices serve as the fundamental building blocks within a power conversion system, exerting significant influence over factors such as system losses and switching speed. The performance of these power devices is primarily characterized by two key parameters: breakdown voltage (VBD) and on-resistance (RON). These characteristics largely depend on the inherent material properties of semiconductors, including carrier mobility and critical electric field. Traditionally, silicon (Si) has been a cornerstone in the realm of power semiconductor devices. However, Si’s material limitations have constrained its further advancement. Consequently, there is an increasing demand for wide bandgap (WBG) semiconductors with bandgaps exceeding 3eV and even ultra-wide bandgap semiconductors with bandgaps exceeding 4.5eV [1]. Among the suite of wide bandgap materials, gallium nitride (GaN) has emerged as a pivotal material for crafting power devices owing to its exceptional material properties, including a wide bandgap of 3.4eV, high critical electric field of 3.3MV/cm, robust resistance to radiation, and impressive saturation velocity [2,3]. In addition to their high voltage handling capabilities, GaN-based power devices offer low RON and minimal conduction losses due to GaN’s electron saturation rate, which is 2.8 times that of silicon [4,5]. Furthermore, GaN devices, especially GaN HEMTs, exhibit high-speed switching performance attributable to their small junction capacitance.

At present, GaN devices are categorized into three voltage ranges [6]. (a) Low (mid)-voltage devices: These devices have a maximum drain-to-source voltage (VDS, max) of less than 200V. They find utility in various fields and are used in applications such as DC–DC power converters, motor drives, class D audio amplifiers, solar microinverters, synchronous rectifications, and LiDAR systems, among others. Depending on specific application requirements, these devices can exhibit RON values ranging from approximately 2mΩ to 200mΩ [7,8,9,10]. (b) High-voltage devices: The VDS, max for these devices goes up to 650V. They are used in applications such as industrial converters, telecommunication servers, servo motor control, power adapters, consumer electronics adapters, class D amplifiers, and data centers [11,12]. (c) Ultra-high-voltage devices: These devices have a VDS, max greater than 1kV. Currently, there are few commercially available GaN power devices in the kV range. The highest voltage rating among commercially available GaN devices is approximately 900V [13], which is used in applications like industrial applications, EV chargers, photovoltaic inverters, and more.

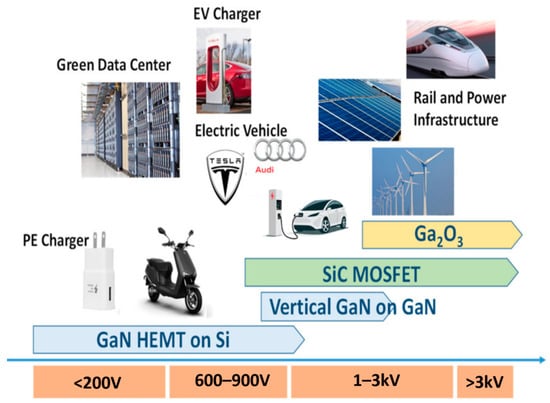

Leading companies such as Transphorm Inc., Infineon Technologies AG, GaN Systems Inc., Panasonic Corporation, Texas Instruments Inc., and others are actively working on introducing GaN devices with voltage ratings exceeding 1kV. The distribution of WBG power devices based on voltage range is illustrated in Figure 1. Currently, several research articles demonstrate the feasibility of GaN power devices rated at 1kV and above [14,15,16]. GaN power devices in the kV range will compete with other WBG power devices, including those based on SiC and Ga2O3, in various applications, such as automotive, industrial, and photovoltaic sectors. However, though some groups have reported achieving high blocking voltage GaN devices, the specific on-resistance (RON-SP) of the GaN device is still much higher than that of the SiC counterpart [17,18].

Figure 1. The distribution of wide bandgap power devices is based on voltage range.

2. GaN Power Devices

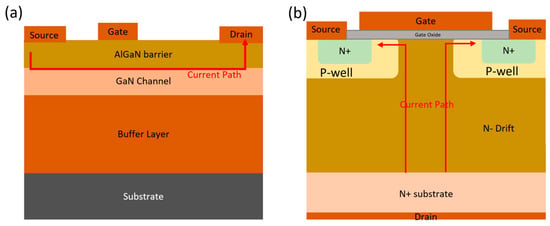

GaN-based power devices are primarily categorized into two fundamental structures: planar (lateral) structure devices and vertical structure devices, as depicted in Figure 2. Planar devices are typically manufactured on Si or SiC substrates, while vertical devices are homoepitaxially grown on GaN substrates. GaN HEMTs are the most commonly employed among GaN power devices. Si substrates are favored in their production to optimize cost-effectiveness and yield. However, epitaxially growing GaN on Si presents considerable challenges due to significant lattice mismatch and a substantial thermal expansion coefficient disparity between the two materials. The lattice mismatch can lead to dislocation propagation and defect generation throughout the GaN epitaxial layers, while thermal mismatch may cause cracking in the GaN layer during cooling after epitaxial growth [20,21,22]. To mitigate defect propagation and attain high-quality, defect-free GaN on Si, a meticulous optimization of the buffer region is imperative. Additionally, it is essential to limit tensile stress during both the growth and cooling phases of the process [23,24].

Figure 2. The schematic structures of (a) a lateral GaN device and (b) a vertical GaN device.

In addition to challenges related to epitaxial layer mismatch, the quality of the top surface becomes a critical concern for achieving optimal performance in lateral GaN devices. The presence of surface states on the AlGaN layer significantly influences the formation of the two-dimensional electron gas (2DEG) [25]. These states can have adverse effects on device performance by unintentionally depleting the 2DEG. This depletion can create a virtual gate between the gate and drain regions, leading to degradation in device performance and reliability. To counteract the depletion of the 2DEG, a well-optimized silicon nitride (SiN) passivation layer is typically employed.

Currently, commercially available GaN HEMTs offer a VBD of approximately 650/900V, coupled with a maximum output DC rating of 150A [26]. These devices find applications across various fields, including onboard battery chargers, high-efficiency power converters, and dense solar panel inverters. However, lateral GaN devices face specific limitations when it comes to scaling VBD and ensuring reliability. These limitations are primarily associated with lateral carrier flow from the source to the drain, with the electron density in the channel being highly sensitive to surface traps and buffer defects. Furthermore, these imperfections in the device can lead to phenomena such as current collapse and dynamic degradation of RON [26,27,28]. The severity of these adverse effects increases as VBD ratings rise. Moreover, the lateral electron transport nature results in a nonuniform distribution of the electric field within the device, leading to a higher electric field concentration in specific regions such as the gate, field plate, or drain edges. This nonuniform electric field distribution may result in premature semiconductor and dielectric breakdown, along with increased electron trapping at the surface. These factors contribute to performance degradation and limit the device’s voltage-blocking potential [28,29].

Furthermore, the VBD of lateral devices is directly proportional to the distance between the gate and drain, which increases both the device size and cost. Another significant concern with lateral GaN HEMT devices is that they are typically normally-ON devices. While various methods exist to create normally-OFF devices, such as using fluorine ion implantation [30,31,32], recess gates [33], p-GaN gates [34], trigate structures [35,36], cascode configurations [37,38], etc., the threshold voltage (VTH) achieved is typically around 1–2V in many cases, including commercial devices. This characteristic makes the device less than ideal for failsafe operation. Lastly, the absence of avalanche capability in lateral GaN devices, possibly due to the lack of a p–n junction between the drain and source regions, which aids in hole extraction during impact ionization, poses challenges in preventing the device from short-term overvoltage failure [39].

To address the limitations of lateral GaN devices, there has been a growing exploration and investigation of vertical GaN devices. The primary distinction between vertical and lateral devices lies in the direction of current flow, as illustrated in Figure 2 with a red arrow for both types. In a vertical device, current flows vertically from the bottom to the top surface (with electrons carrying the current from top to bottom) or in parallel with the direction of the GaN epitaxial layers. Consequently, current conduction occurs through the surface channel and then through a bulk drain drift region formed by a homoepitaxial GaN layer on a GaN substrate. Unlike lateral devices, vertical devices do not have a 2DEG drain drift region near the surface or a defect-rich buffer layer, as found in GaN HEMTs. As a result, there is less degradation in dynamic RON, which often occurs due to trapped impurity charges or bulk traps resulting from lattice mismatch [40]. One of the most significant advantages of vertical devices over lateral ones is their VBD. The VBD of a vertical device can be increased by augmenting the thickness of the N-drift layer, which is typically a low-doped or unintentionally doped GaN epitaxial layer (also known as the GaN N-drift layer). Consequently, this makes the VBD independent of the lateral size of the device. Moreover, a vertical GaN device can achieve a VTH ranging from around 5 to 15V, making it well-suited for high-power applications [41].

Another advantage of vertical GaN devices is their ability to exhibit avalanche breakdown, enhancing device reliability and potentially eliminating the need for overdesigning the device [42,43,44]. During transients, avalanche breakdown serves as a failsafe operation, allowing the device to operate closer to its material limits [45]. The VBD of a vertical GaN device can be significantly higher because the drain is located at the bottom of the device. When a high voltage is applied at the terminal, the electric field is evenly distributed throughout the device in a vertical direction, unlike lateral devices that experience electric field spikes at the gate edge [46]. This even distribution of the electric field within the device, away from the surface, can mitigate the effects of current collapse by countering the influence of surface states and thus slowing down the occurrence of current collapse [47,48]. Vertical GaN devices also offer the advantage of easily increasing power density. Since there are no electric field spikes, unlike lateral devices, there is no need for the field plate structure, which typically increases gate leakage spacing, to enhance breakdown performance. This makes it simpler to improve wafer utilization and boost power density [49].

The nFET operation of the vertical device is controlled by two primary p–n junctions, forming gate–source, and gate–drain diodes. Avalanche breakdown occurs when the drain–source voltage of the device exceeds its VBD. Initially, avalanche breakdown occurs through the reverse-biased drain–gate diode region, leading to an increase in the gate–source voltage and the opening of the channel region. Unlike lateral GaN devices, avalanche breakdown in vertical devices remains within the short-term power dissipation limits. Furthermore, energy dissipation occurs within the drift region of the device rather than on the surface (a sensitive region). This feature helps protect the device from transient spikes and other abnormal operating conditions. In a vertical GaN device, the epitaxial layer is grown homoepitaxially on the native GaN substrate, eliminating issues related to lattice or thermal expansion coefficient mismatches. The performance of the vertical GaN device remains unaffected by defect densities and manufacturing challenges such as wafer bow, warp, cracking, etc. Consequently, vertical GaN devices offer high reliability, yield, and, ultimately, reduced costs compared to lateral devices. Despite the significant potential of vertical GaN in dominating power devices, the current landscape still heavily relies on lateral device structures due to the complexities involved in preparing vertical devices and the high cost of GaN substrates [50].

A notable breakthrough in GaN devices is the introduction of GaN on SiC. GaN on SiC is a device that combines the advantages of both materials. The remarkable thermal conductivity of SiC, outperforming GaN alone, facilitates efficient heat dissipation, fostering enhanced device performance and durability. These devices are characterized by high power density and high-frequency response, attributes that lend themselves perfectly to applications in high-frequency electronics like radars and satellite communications. The symbiotic relationship between GaN and SiC, marked by minimal lattice mismatch and thermal stress, ensures devices that are reliable over extended operational timelines. This integration is known to reduce parasitic capacitances and resistances, paving the way for quicker device switching and diminished energy losses [51,52].

Despite the obvious advantages, SiC substrates tend to be more expensive compared to alternatives like Si or sapphire, which can escalate the overall device cost. The nuanced processes involved in the epitaxial growth of GaN on SiC lead to defects, which could compromise device efficiency. The demand for large-diameter SiC wafers often outstrips the supply, potentially hindering widespread commercial adoption and mass production [53,54]. A major issue with these devices is their compromised off-state performance, characterized by increased leakage and reduced VBD. Studies suggest that these defects can intensify leakage by acting as electron–hole pair generators under strong electric fields. As illustrated in some research, when exposed to high electric fields, these defects create holes that can accumulate at the boundary between the dielectric and the semiconductor. This accumulation can then intensify the field in the oxide, leading to a potential device failure. Interestingly, in comparisons using trench MOSFETs, devices on bulk GaN outperform those on alternative materials [55,56]. GaN on SiC in vertical devices is a tapestry of clear advantages punctuated by challenges.

This entry is adapted from the peer-reviewed paper 10.3390/mi14101937

This entry is offline, you can click here to edit this entry!