The exceptional electronic, optical and mechanical properties of graphene can lead to revolutionary new devices. Since the transfer process of graphene from a dedicated growth substrate to another substrate is prone to induce defects and contamination and can increase costs, there is a large interest in methods for growing graphene directly on silicon wafers. It has become clear that chemical vapor deposition (CVD) is the most promising process to guarantee large-area high-quality graphene.

- graphene synthesis

- CVD

- nanofabrication

- thin films

- silicon technology

1. Introduction

2. Transfer-Based Integration

3. Transfer-Free Integration

4. Conclusion and Outlook

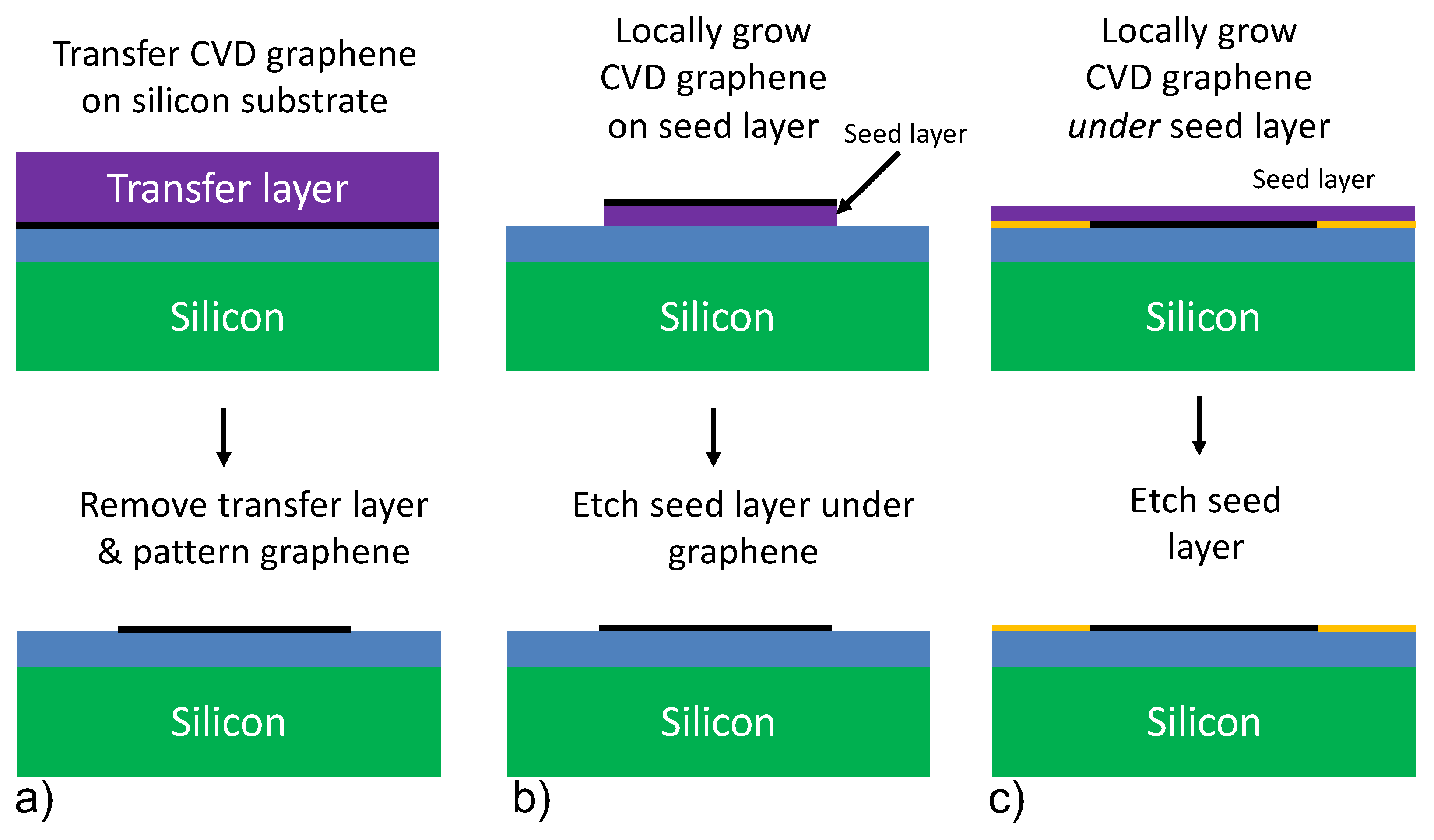

Due to the difficulties related to transfer-based integration of graphene, transfer-less or direct growth approaches for integrating graphene on silicon and CMOS have been gaining growing attention. The drawback of these transfer-less schemes is however that the growth temperatures are so high that they will lead to detrimental diffusion of the p and n-type dopants in CMOS transistors. For that reason other 2D materials, that can be grown directly on silicon substrates, are also receiving increasing attention as potential materials for CMOS integration and might thus might have a better chance for playing an important role in next-generation nano-electronic devices.

References

- Akinwande, D.; Huyghebaert, C.; Wang, C.H.; Serna, M.I.; Goossens, S.; Li, L.J.; Wong, H.S.P.; Koppens, F.H. Graphene and two-dimensional materials for silicon technology. Nature 2019, 573, 507–518.

- Neumaier, D.; Pindl, S.; Lemme, M.C. Integrating graphene into semiconductor fabrication lines. Nat. Mater. 2019, 18, 525–529.

- Ullah, S.; Yang, X.; Ta, H.Q.; Hasan, M.; Bachmatiuk, A.; Tokarska, K.; Trzebicka, B.; Fu, L.; Rummeli, M.H. Graphene transfer methods: A review. Nano Res. 2021, 14, 3756–3772.

- Wagner, S.; Weisenstein, C.; Smith, A.D.; Östling, M.; Kataria, S.; Lemme, M.C. Graphene transfer methods for the fabrication of membrane-based NEMS devices. Microelectron. Eng. 2016, 159, 108–113.

- Zhu, W.; Low, T.; Perebeinos, V.; Bol, A.A.; Zhu, Y.; Yan, H.; Tersoff, J.; Avouris, P. Structure and elctronic transport in graphene wrinkles. Nano Lett. 2012, 12, 3431–3436.

- Grachova, Y.; Vollebregt, S.; Lacaita, A.L.; Sarro, P.M. High Quality Wafer-scale CVD Graphene on Molybdenum Thin Film for Sensing Application. Procedia Eng. 2014, 87, 1501–1504.

- Ricciardella, F.; Vollebregt, S.; Polichetti, T.; Alfano, B.; Massera, E.; Sarro, P.M. High sensitive gas sensors realized by a transfer-free process of CVD graphene. In Proceedings of the 2016 IEEE SENSORS, Orlando, FL, USA, 30 October–3 November 2016; pp. 1–3.

- Vollebregt, S.; Alfano, B.; Ricciardella, F.; Giesbers, A.J.M.; Grachova, Y.; van Zeijl, H.W.; Polichetti, T.; Sarro, P.M. A transfer-free wafer-scale CVD graphene fabrication process for MEMS/NEMS sensors. In Proceedings of the 2016 IEEE 29th International Conference on Micro Electro Mechanical Systems (MEMS), Shanghai, China, 24–28 January 2016; pp. 17–20.

- Vollebregt, S.; Dolleman, R.J.; van der Zant, H.S.J.; Steeneken, P.G.; Sarro, P.M. Suspended graphene beams with tunable gap for squeeze-film pressure sensing. In Proceedings of the 2017 19th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Kaohsiung, Taiwan, 18–22 June 2017; pp. 770–773.

- Romijn, J.; Dolleman, R.J.; Singh, M.; van der Zant, H.S.J.; Steeneken, P.G.; Sarro, P.M.; Vollebregt, S. Multi-layer graphene pirani pressure sensors. Nanotechnology 2021, 32, 335501.

- McNerny, D.Q.; Viswanath, B.; Copic, D.; Laye, F.R.; Prohoda, C.; Brieland-Shoultz, A.C.; Polsen, E.S.; Dee, N.T.; Veerasamy, V.S.; Hart, A.J. Direct fabrication of graphene on SiO2 enabled by thin film stress engineering. Sci. Rep. 2014, 4, 5049.

- Kang, B.J.; Mun, J.H.; Hwang, C.Y.; Cho, B.J. Monolayer graphene growth on sputtered thin film platinum. J. Appl. Phys. 2009, 106, 104309.

- Sutter, P.; Sadowski, J.T.; Sutter, E. Graphene on Pt (111): Growth and substrate interaction. Phys. Rev. B 2009, 80, 245411.

- Gao, M.; Pan, Y.; Huang, L.; Hu, H.; Zhang, L.; Guo, H.; Du, S.; Gao, H.J. Epitaxial growth and structural property of graphene on Pt (111). Appl. Phys. Lett. 2011, 98, 033101.

- Gao, T.; Xie, S.; Gao, Y.; Liu, M.; Chen, Y.; Zhang, Y.; Liu, Z. Growth and atomic-scale characterizations of graphene on multifaceted textured Pt foils prepared by chemical vapor deposition. ACS Nano 2011, 5, 9194–9201.

- Addou, R.; Batzill, M. Defects and domain boundaries in self-assembled terephthalic acid (TPA) monolayers on CVD-grown graphene on Pt (111). Langmuir 2013, 29, 6354–6360.

- Lee, B.J.; Jeong, G.H. Comparative study on graphene growth mechanism using Ni films, Ni/Mo sheets, and Pt substrates. Appl. Phys. A 2014, 116, 15–24.

- Ma, T.; Ren, W.; Liu, Z.; Huang, L.; Ma, L.P.; Ma, X.; Zhang, Z.; Peng, L.M.; Cheng, H.M. Repeated growth–etching–regrowth for large-area defect-free single-crystal graphene by chemical vapor deposition. ACS Nano 2014, 8, 12806–12813.

- Weatherup, R.S.; Shahani, A.J.; Wang, Z.J.; Mingard, K.; Pollard, A.J.; Willinger, M.G.; Schloegl, R.; Voorhees, P.W.; Hofmann, S. In situ graphene growth dynamics on polycrystalline catalyst foils. Nano Lett. 2016, 16, 6196–6206.

- Preobrajenski, A.; Ng, M.L.; Vinogradov, A.; Mårtensson, N. Controlling graphene corrugation on lattice-mismatched substrates. Phys. Rev. B 2008, 78, 073401.

- Xu, Z.; Buehler, M.J. Interface structure and mechanics between graphene and metal substrates: A first-principles study. J. Phys. Condens. Matter 2010, 22, 485301.

- Gao, M.; Pan, Y.; Zhang, C.; Hu, H.; Yang, R.; Lu, H.; Cai, J.; Du, S.; Liu, F.; Gao, H.J. Tunable interfacial properties of epitaxial graphene on metal substrates. Appl. Phys. Lett. 2010, 96, 053109.

- Adamska, L.; Lin, Y.; Ross, A.J.; Batzill, M.; Oleynik, I.I. Atomic and electronic structure of simple metal/graphene and complex metal/graphene/metal interfaces. Phys. Rev. B 2012, 85, 195443.

- Verguts, K.; Coroa, J.; Huyghebaert, C.; De Gendt, S.; Brems, S. Graphene delamination using ‘electrochemical methods’: An ion intercalation effect. Nanoscale 2018, 10, 5515–5521.

- Verguts, K.; Defossez, Y.; Leonhardt, A.; De Messemaeker, J.; Schouteden, K.; Van Haesendonck, C.; Huyghebaert, C.; De Gendt, S.; Brems, S. Growth of millimeter-sized graphene single crystals on Al2O3 (0001)/Pt (111) template wafers using chemical vapor deposition. ECS J. Solid State Sci. Technol. 2018, 7, M195.