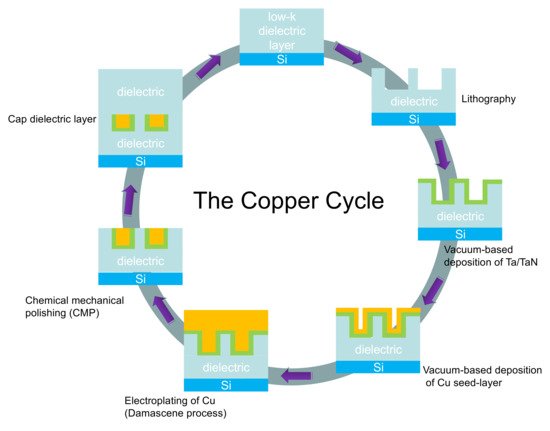

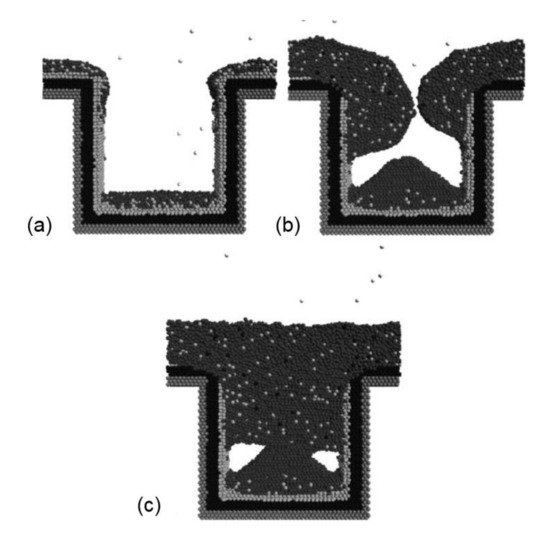

The barrier layer in Cu technology is essential to prevent Cu from diffusing into the dielectric layer at high temperatures; therefore, it must have a high stability and good adhesion to both Cu and the dielectric layer. In the past three decades, tantalum/tantalum nitride (Ta/TaN) has been widely used as an inter-layer to separate the dielectric layer and the Cu. However, to fulfill the demand for continuous down-scaling of the Cu technology node, traditional materials and technical processes are being challenged. Direct electrochemical deposition of Cu on top of Ta/TaN is not realistic, due to its high resistivity. Therefore, pre-deposition of a Cu seed layer by physical vapor deposition (PVD) or chemical vapor deposition (CVD) is necessary, but the non-uniformity of the Cu seed layer has a devastating effect on the defect-free fill of modern sub-20 or even sub-10 nm Cu technology nodes. New Cu diffusion barrier materials having ultra-thin size, high resistivity and stability are needed for the successful super-fill of trenches at the nanometer scale. In this review, we briefly summarize recent advances in the development of Cu diffusion-proof materials, including metals, metal alloys, self-assembled molecular layers (SAMs), two-dimensional (2D) materials and high-entropy alloys (HEAs). Also, challenges are highlighted and future research directions are suggested.

- Cu diffusion barrier

- platinum group metals

- 2D materials

- self-assembled monolayers

1. Introduction

2. Cu Interconnects and Diffusion Barrier Materials

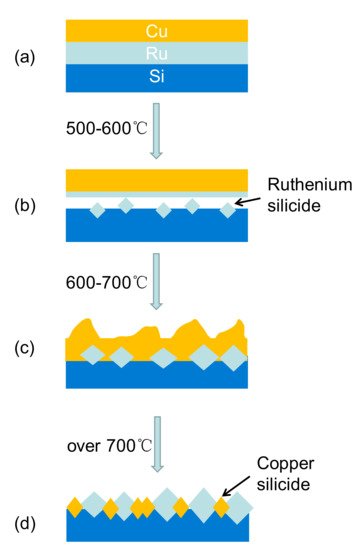

3. Platinum Group Metals (PGM)-Based Materials

This entry is adapted from the peer-reviewed paper 10.3390/ma13215049