Your browser does not fully support modern features. Please upgrade for a smoother experience.

Please note this is a comparison between Version 3 by Jessie Wu and Version 4 by Jessie Wu.

This entry describes that recent advances of memristive system-based image processing are presented.

- memristive systems

1. Introduction

With the advent of the Internet of Things, cloud computing, and the big data era, there has been explosive growth in the scale of information. However, the physical separation among perception, computation, and storage in the conventional computing architecture requires frequent data shuttling among the units, thereby causing significant system consumption and speed loss and making it difficult to meet the requirements of information analysis and processing [1][2][3]. Therefore, developing new electronic components for intelligent processing systems that are closer to the structure and function of biological brains has become a hot research topic in the fields of modern electronic circuits and image processing [4][5][6].

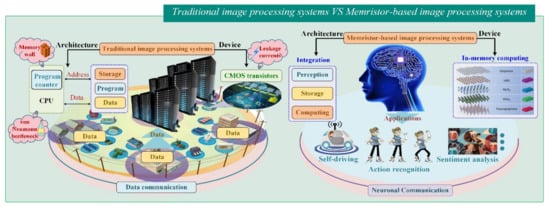

Image processing technology, which aims to automatically acquire high-level and abstract information from images, after which it simulates how human eyes work with such information, has become increasingly useful in human life and social production. Exploring the basic structure of human brains, simulating their working mechanisms, and establishing neural network models that integrate perception, storage, and computation as a whole have gradually become research hotspots in the fields of image processing and cognitive computing [7]. The current mainstream neural network models can simulate the reasoning and learning functions of human brains to a certain extent, and they have shown some potential in image processing [8]. However, they are confined to certain types and structures with limited processing capabilities. Additionally, the existing ones lack the process of information perception, transmission, and storage prior to the processing stage. Furthermore, the hardware for neural networks is essential to truly realize the conversion from theoretical studies of brain cognition to new technologies of brain-computer intelligence. Nevertheless, most of the current research focuses on the theoretical analysis of the network structures and algorithms, and the research on implementation schemes for neural network hardware is still in its infancy [9][10][11]. Influenced by factors, such as device size, energy consumption, and integrability, conventional implementation schemes for image processing cannot well trade-off the relationship between speed, accuracy, and system consumption [12][13][14]. We schematically compare the traditional image processing systems and memristor-based image processing system as shown in Figure 1. From the perspective of the device, leakage currents become a problem when the channel length and the gate dielectric thickness of a transistor get closer to the scaling limit [3]. With respect to the architecture, the data transfer between processors and memory units significantly reduces both speed and energy efficiency (referred to as the ‘von Neumann bottleneck’). Furthermore, the performance mismatch between the memory and processing units leads to great latency (also called the ‘memory wall’).

Figure 1. The comparation between the traditional image processing systems and memristor-based image processing system.

The successful preparation of memristors provides a fresh perspective on the hardware implementation of artificial neural networks. It was proposed by Leon Chua, a scientist at the University of California, Berkeley [15] and discovered by Hewlett-Packard (HP) laboratories in 2008 as the fourth fundamental electronic component after the resistor, capacitor, and inductor [16]. Experiments have shown that the memristor has properties, such as non-volatility, variable resistance, nanoscale size, threshold characteristics, low power consumption, and synapse-like structure [17][18][19]. In particular, by taking full advantage of being synapse-like, the memristor can be used as an “electronic synapse” or an “artificial synapse” in the hardware design of neural networks [20]. Further, after choosing a proper memristor model to simulate the weight of the neural network, a more integrated architecture for hardware implementation can be constructed and applied to different image processing tasks [21][22]. Compared with conventional artificial neural networks, the memristive ones incorporate powerful perception ability, massive storage capacity, and intelligent processing mechanisms to enable deeper analysis and exploration, which are expected to solve slow training speed and insufficient online processing capability in image processing [23][24][25].

2. Image Processing Based on Memristive Neural Networks

The successful preparation of memristors brings new ideas for simulating the cognitive functions of artificial synapses. By applying memristive synapses to the hardware implementation of neural networks, a new type of neural network with high integration can be built. It possesses powerful image processing capabilities and plays an important role in fields with high computational complexity, such as image recognition, classification, and segmentation.

2.1. Image Recognition Based on Memristive Neural Networks

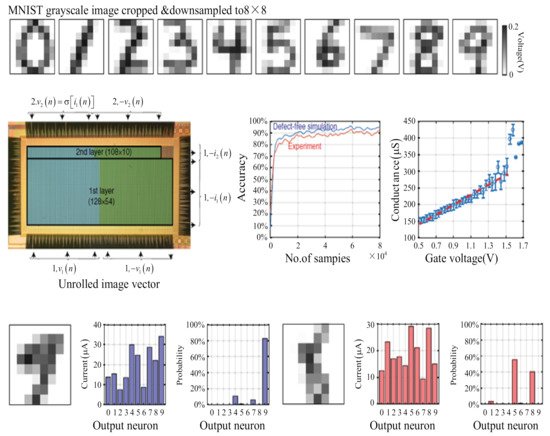

In the literature [26], an impulsive neural network based on memristors was constructed in which the memristive synapses used STDP rules to update the weights, and the memristive neurons adopted the “winner-take-all” strategy to complete the task of handwriting recognition. It was found that its recognition accuracy could reach 83%. A study conducted by Yakopcic et al. [27] presented a memristor-based convolutional neural network to perform convolutional operations using memristor crossbar arrays, and the accuracy of its handwritten digit recognition reached 94%. Furthermore, a transformation method for neural network models was brought forward [28], as shown in Figure 2.

Figure 2. Handwriting recognition based on the ReRAM array.

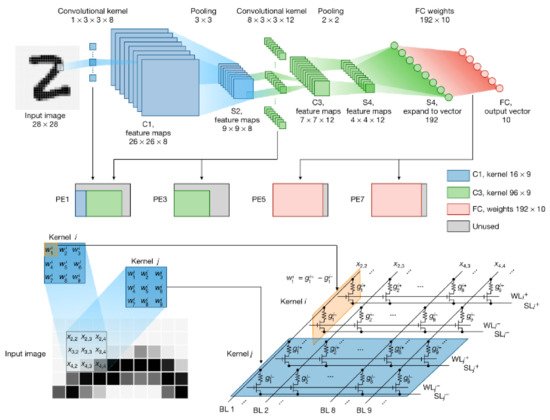

Specifically, the method of sparsity was taken to divide the original neural network into appropriately sized sub-networks. The limited hardware accuracy was solved by quantizing the input data and somewhat improved to approximately 99.8% from the software side. In the study [29], a 1M structured memristive synapse was introduced to the memristor-based multilayer neural network, and an adaptive backpropagation algorithm was applied to train the neural networks, thereby achieving character recognition. Kang Jinfeng’s team at Peking University [30] reported a memristor-based binary neural network. It was trained online, its weight update was achieved using the 2T2R structure of the memristive synapse, and its correctness and effectiveness were verified on the MNIST dataset with a recognition accuracy of 97.4%. In addition, Hu et al. [22] used 2 phase-change memories to construct artificial synapses, based on which a 3-layer perceptron network was built, and they proved its correctness on the MNIST dataset with a recognition accuracy of 82.2%. For Wang et al. [31], they constructed a memristor-based convolutional neural network, which was significantly improved in terms of array area and energy efficiency compared with previous ones for the handwriting recognition task. In 2020, a research team from Tsinghua University [32] designed a memristor-based convolutional neural network (see Figure 3). Meanwhile, a hybrid training method was suggested to enhance the robustness of the network, and the handwriting recognition task realized an accuracy of over 96%.

Figure 3. Five-layer mCNN with memristor convolver.

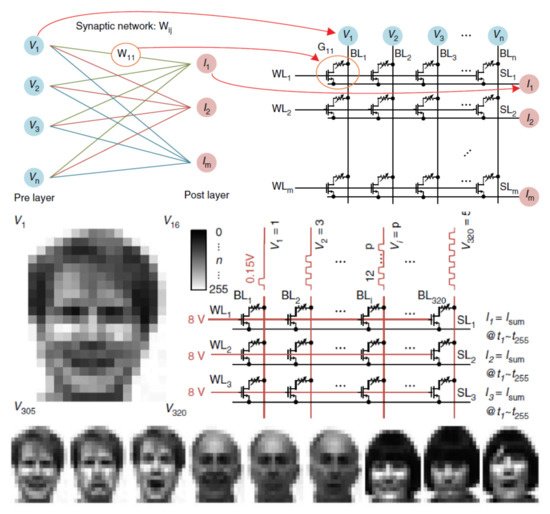

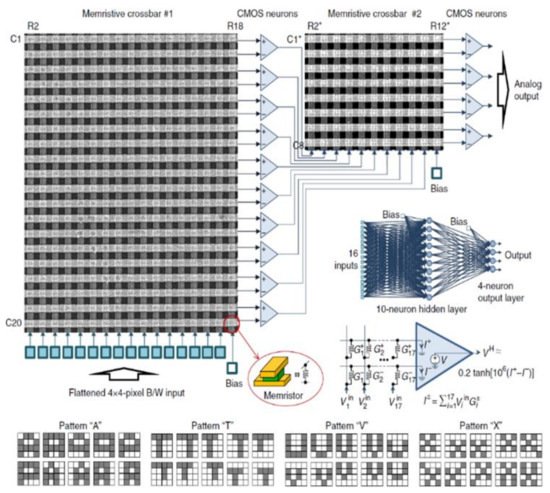

In addition, memristor-based neural networks have been applied to other image recognition tasks. For instance, Professor Wu Huaqiang and his team members from Tsinghua University constructed a multilayer perceptron neural network based on 1T1R memristive synapses [33], as shown in Figure 4. The network achieved grey scale face image recognition from the Yale Face Database through online learning, and the recognition rate could reach 88.08% for 9000 test images with noise added. Other researchers [34] investigated a hierarchical temporal memory (HTM) network based on memristors, which applied sparse distributed representations to obtain spatial information of input signals, after which they used parallel learning to adjust the network weights and finally verified the correctness and effectiveness of the network through face recognition tasks. As for the memristor-based probabilistic neural network [35], it carried out product multiplication using memristor crossbar arrays as well as normalization operations on weights to reduce the complexity of the circuit. The network was validated on the Iris Flower dataset with a recognition accuracy of 98%. Furthermore, the multilayer perceptron neural network studied by Yu et al. [36] showed increased adaptive capability by introducing nonlinear features in the learning process and superior performance on general datasets, such as MNIST, Iris, and Car Evaluation.

Figure 4. Face recognition task is realized in 1T1R array.

2.2. Image Classification Based on Memristive Neural Networks

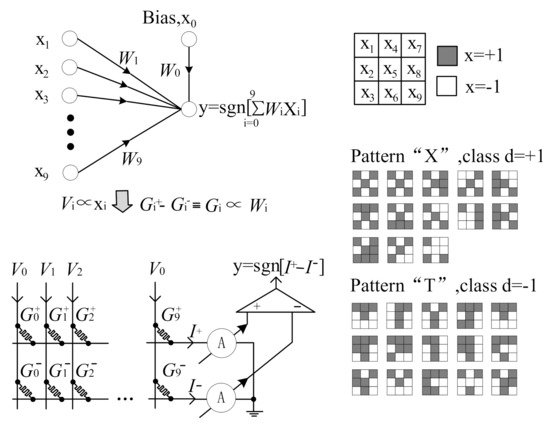

In 2013, Alibart et al. [37] successfully prepared a TiO2−x-based memristor, after which they developed a single-layer perceptron (SLP) neural network based on the TiO2−x memristor crossbar array to achieve image classification. Its circuit structure is displayed in Figure 5.

Figure 5. Single-layer perceptron network memristor circuit.

Another (SLP) neural network was made based on 2M memristive synapses [10], and its circuit structure is presented in Figure 6. The network, which was trained using delta rules, achieved the classification of 3 × 3-pixel black-and-white images. Professor Strukov’s team at the University of California, Santa Barbara [38] prepared a 20 × 20 memristor crossbar array, as depicted in Figure 7. The array adopted TiO2−x and Al2O3 as the functional and stacked layers, respectively, after which it was interconnected with traditional CMOS peripheral circuits, thereby constructing an SLP neural network to achieve the image classification with an accuracy of more than 97%.

Figure 6. Single layer perceptron implemented using 10 × 6 memristor crossbar array.

Figure 7. Three-layer fully connected perceptron network realized though Pt/Al2O3/TiO2−x/Ti/Pt memristor arrays.

Wang et al. [39] prepared a three-dimensional structured memristor and applied it to image classification, which improved the operational efficiency of the algorithm and opened a new path for the in-depth integration of computer vision and novel nanodevices. Additionally, a memory computing framework based on memristors was proposed by Zhang et al. in 2021 [40], which used a greedy search algorithm to improve the robustness and anti-interference capability of the system, and its accuracy reached 92.3% on the classification tasks involving the CIFAR-10 dataset.

2.3. Image Segmentation Based on Memristive Neural Networks

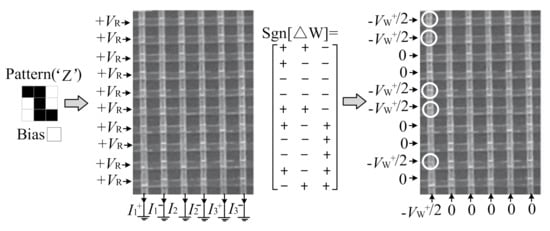

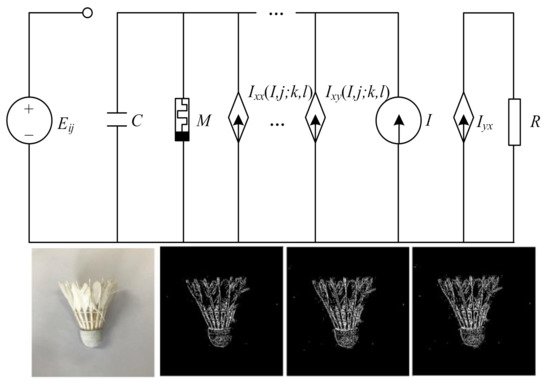

As early as 2014, Myonglae et al. [41] proposed a memristor-based visual recognition system, where the system used a programmable gate array to convert image signals into pulse signals and performed weight updates based on STDP learning rules. As a result, the foreground and background segmentation of figure images from “0” to “9” were achieved. One year later, Chiu and his team members [42] constructed a differential 2R crossbar array, which applied RRAM as a cache to reduce system energy consumption, and they verified its correctness and effectiveness using image segmentation tasks. In the literature [43], a fully convolutional neural network based on memristors was introduced. It utilized voltage selectors and memristor arrays to construct its max-pooling layers as well as a sliding window approach to enhance operation efficiency. Moreover, the weight updates of memristor arrays were implemented through the ex-situ training method, and the effectiveness of the proposed network was finally verified through image segmentation. The study [44] designed a memristor-based cell neural network based on the fractional-order calculus theory, as illustrated in Figure 8.

Figure 8. Memristor-based cell neural network.

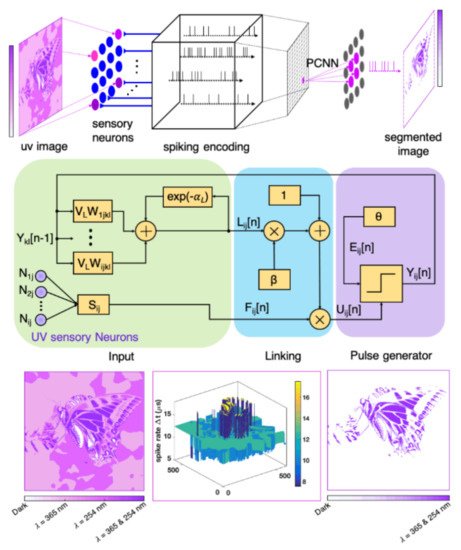

In the process of image edge extraction, it took the fractional-order control method to increase the high-frequency information and retain more low-texture information. The simulation results proved that the edge images extracted by this network had more complete and clear contour information and richer texture detail information. Another example is the prepared memristor with NbOx as its functional layer [45]. An artificial sensory neuron was constructed, then in combination with an InGaZnO4 optical sensor (see Figure 9), which encoded optical information into impulses, image segmentation in complex backgrounds was achieved by such a pulse-coupled neural network. It is believed that this study has paved the way for the integration of neuromorphology and bioelectronics. In 2021, Chen et al. [46] proposed an efficient memristor-based fully convolutional neural network, which adopted a convolutional kernel-first (CKF) algorithm to achieve effective parameter pruning, thereby significantly reducing circuit power consumption and demonstrating high accuracy and adaptiveness for medical image segmentation tasks.

Figure 9. Impulse coupled neural network based on memristor.

2.4. Others

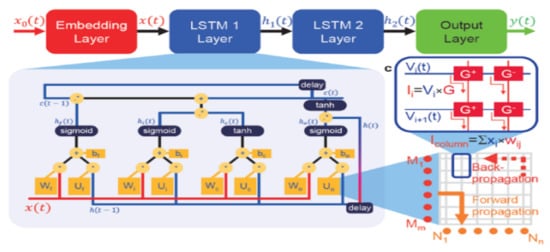

Tsai et al. [47] reported a long short-term memory network, which mapped and programmed the network weights into the phase-change memory devices, as demonstrated in Figure 10. Compared to other methods, this network realized the software-equivalent text prediction as well as a larger improvement in the accuracy of weight mapping and text prediction.

Figure 10. Realization method of long short-term memory network based on phase-change memory device unit.

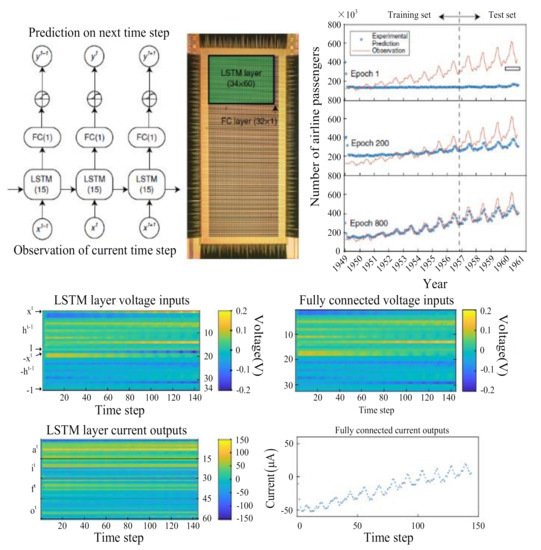

Another long short-term memory network was built on a 128 × 64 1T1R memristor array [48], as shown in Figure 11. Through utilizing the memristor arrays to store synaptic weights for different time steps, the network performed the prediction task of the number of global airline passengers and the recognition task of human gait, and it verified the feasibility of the memristor-based long short-term memory neural network in performing tasks, such as linear regression and pattern recognition.

Figure 11. LSTM network based on memristor synaptic array.

Moreover, Farkhani et al. [49] designed a neuromorphic computing system based on spintronic memristors, where the read circuit was replaced with a proposed real-time sensing circuit, and the input signals were turned into the switching of magnetic moments, thereby substantially reducing circuit energy consumption, providing system operational efficiency, and achieving the real-time tracking of targets. As for the study [50], the chaotic trajectories of memristive circuits were included, which combined the homotopy analysis method (HAM) and multi-objective optimization (MO) to tackle the high computational complexity and low computational efficiency of traditional analysis methods.

In this paper, the architectural characteristics of several image processing algorithms based on memristive neural networks are comprehensively summarized, including their input coding patterns, weight representations and the data types of interlayer communication. The specific comparative information is summarized in Table 14.

Table 14. Comparative information of memristive neural network-based image processing.

| Reference | Architectural Characteristics of Image Processing Algorithms Based on Memristive Neural Networks | ||

|---|---|---|---|

| Input Coding | Weight Representation | Neural Network Communication | |

| [51] | Amplitude Encoding/Time Encoding Analogue Signal | Differential Amplifier | Multi-precision |

| [52] | Amplitude Encoding Analogue Signal | Multi-precision | MSB |

| [38] | Amplitude Encoding Analogue Signal | Differential Amplifier | Multi-precision |

| [40] | Amplitude Encoding Analogue Signal | Differential Amplifier | Multi-precision |

| [53] | Amplitude Encoding Analogue Signal | Peripheral Circuit Processing | MSB |

The above key research questions will provide references for building the next generation of novel memristive neural networks with integrated perception-storage-computation architectures.

2.5. Summary

With the expanded research in nanomaterials science and image processing technology, image processing based on memristive neural networks has become one of the hot issues in the study on neural network hardware implementation schemes. Currently, there are the following problems that must be solved timely.

- (1)

-

The existing memristive synaptic circuits can only simulate the basic functions and behavioural characteristics of biological synapses, and they lack enough theoretical support from computational neuroscience. Therefore, it is crucial to design a fully functional and simple structured memristive synaptic circuit, which can address the problems of insufficient portray, unclear mechanism, and single plasticity of the conventional ones.

- (2)

-

There is the accumulation of computational errors in memristor-based neural network circuits, which is mainly owing to the discrete nature of memristors, and it is difficult to avoid at the device level. Therefore, designing a newly structured memristor crossbar array that offsets the accumulated errors can provide a new perspective for the hardware implementation of neural networks.

- (3)

-

The current research on image processing based on memristive neural networks is still stuck in the simulation of existing artificial neural networks. Therefore, the next research hotspot will involve taking both the advantages of neurocomputing science and image processing studies, exploring brain-inspired neural network training algorithms, and building memristive neural networks with brain-like memory.

References

- Chu, M.; Kim, B.; Park, S.; Hwang, H.; Jeon, M.; Lee, B.H.; Lee, B.G. Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. IEEE Trans. Ind. Electron. 2015, 62, 2410–2419.

- Wen, S.; Wei, H.; Zeng, Z.; Huang, T. Memristive fully convolutional network: An accurate hardware image-segmentor in deep learning. IEEE Trans. Emerg. Top. Comput. Intell. 2018, 2, 324–334.

- Liu, Q.; Wang, L.; Yang, J.; Wang, Y.; Duan, S. Fusion of image storage and operation based on ag-chalcogenide memristor with synaptic plasticity. J. Circuits Syst. Comput. 2017, 26, 1614.

- Li, C.; Hu, M.; Li, Y.; Jiang, H.; Ge, N.; Montgomery, E.; Zhang, J.; Song, W.; Dávila, N.; Graves, C.E.; et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 2018, 1, 52–59.

- Yu, Y.; Adu, K.; Tashi, N.; Anokye, P.; Wang, X.; Ayidzoe, M.A. RMAF: Relu-Memristor-Like Activation Function for Deep Learning. IEEE Access 2020, 8, 72727–72741.

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 2010, 10, 1297–1301.

- Schmidhuber, J. Deep Learning in neural networks: An overview. Neural Netw. 2015, 61, 85–117.

- Ji, X.; Qi, D.; Dong, Z.; Lai, C.S.; Zhou, G.; Hu, X. TSSM: Three-state switchable memristor model based on Ag/TiOx nanobelt/Ti configuration. Int. J. Bifurc. Chaos 2021, 31, 2130020.

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive devices for computing. Nat. Nanotechnol. 2013, 8, 13–24.

- Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.D.; Adam, G.C.; Likharev, K.K.; Strukov, D.B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 2015, 521, 61–64.

- Pi, S.; Li, C.; Jiang, H.; Xia, W.; Xin, H.; Yang, J.J.; Xia, Q. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat. Nanotechnol. 2019, 14, 35–39.

- Gokmen, T.; Onen, M.; Haensch, W. Training deep convolutional neural networks with resistive cross-point devices. Front. Neurosci. 2017, 11, 538.

- Esser, S.K.; Merolla, P.A.; Arthur, J.V.; Cassidy, A.S.; Appuswamy, R.; Andreopoulos, A.; Berg, D.J.; McKinstry, J.L.; Melano, T.; Barch, D.R.; et al. Convolutional networks for fast, energy-efficient neuromorphic computing. Proc. Natl. Acad. Sci. USA 2016, 113, 11441–11446.

- Choi, S.; Shin, J.H.; Lee, J.; Sheridan, P.; Lu, W.D. Experimental demonstration of feature extraction and dimensionality reduction using memristor networks. Nano Lett. 2017, 17, 3113–3118.

- Chua, L.O. Memristor—The missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519.

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83.

- Zhang, C.; Ye, W.B.; Zhou, K.; Chen, H.Y.; Yang, J.Q.; Ding, G.; Chen, X.; Zhou, Y.; Zhou, L.; Li, F.; et al. Bioinspired artificial sensory nerve based on nafion memristor. Adv. Funct. Mater. 2019, 29, 1970133.

- Hu, L.; Fu, S.; Chen, Y.; Cao, H.; Liang, L.; Zhang, H.; Gao, J.; Wang, J.; Zhuge, F. Ultrasensitive memristive synapses based on lightly oxidized sulfide films. Adv. Mater. 2017, 29, 6927.

- Xu, W.; Lee, Y.; Min, S.Y.; Park, C.; Lee, T.W. Simple, inexpensive, and rapid approach to fabricate cross-shaped memristors using an inorganic-nanowire-digital-alignment technique and a one-step reduction process. Adv. Mater. 2016, 28, 527–532.

- Dong, Z.; Lai, C.S.; He, Y.; Qi, D.; Duan, S. Hybrid dual-complementary metal-oxide-semiconductor/memristor synapse-based neural network with its applications in image super-resolution. IET Circuits Devices Syst. 2019, 13, 1241–1248.

- Sheri, A.M.; Hwang, H.; Jeon, M.; Lee, B.G. Neuromorphic character recognition system with two PCMO memristors as a synapse. IEEE Trans. Ind. Electron. 2014, 61, 2933–2941.

- Hu, M.; Graves, C.E.; Li, C.; Li, Y.; Ge, N.; Montgomery, E.; Davila, N.; Jiang, H.; Williams, R.S.; Yang, J.J.; et al. Memristor-Based analog computation and neural network classification with a dot product engine. Adv. Mater. 2018, 30, 5914.

- Xie, L.; Nguyen, H.A.D.; Yu, J.; Kaichouhi, A.; Taouil, M.; Alfailakawi, M.; Hamdioui, S. Scouting logic: A novel memristor-based logic design for resistive computing. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, ISVLSI, Bochum, Germany, 3–5 July 2017; IEEE Computer Society: Bochum, Germany, 2017; pp. 176–181.

- Kvatinsky, S.; Satat, G.; Wald, N.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. Memristor-based material implication (IMPLY) logic: Design principles and methodologies. IEEE Trans. Very Large Scale Integr. Syst. 2014, 22, 2054–2066.

- James, A.P. Memristor threshold logic: An overview to challenges and applications. arXiv 2016, arXiv:1612.01711.

- Wu, X.; Saxena, V.; Zhu, K. Homogeneous spiking neuromorphic system for real-world pattern recognition. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 254–266.

- Yakopcic, C.; Alom, M.Z.; Taha, T.M. Memristor crossbar deep network implementation based on a Convolutional neural network. In Proceedings of the 2016 International Joint Conference on Neural Networks (IJCNN), Vancouver, BC, Canada, 24–29 July 2016; Institute of Electrical and Electronics Engineers Inc.: Vancouver, BC, Canada, 2016; Volume 2016, pp. 963–970.

- Li, C.; Hu, M.; Li, Y.; Jiang, H.; Ge, N.; Montgomery, E.; Zhang, J.; Song, W.; Dávila, N.; Graves, C.E.; et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 2018, 1, 52–59.

- Zhang, Y.; Wang, X.; Friedman, E.G. Memristor-based circuit design for multilayer neural networks. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 677–686.

- Zhou, Z.; Huang, P.; Xiang, Y.C.; Shen, W.S.; Zhao, Y.D.; Feng, Y.L.; Gao, B.; Wu, H.Q.; Qian, H.; Liu, L.F.; et al. A new hardware implementation approach of BNNs based on nonlinear 2T2R synaptic cell. Tech. Dig. Int. Electron Devices Meet. IEDM 2019, 18, 71–74.

- Wang, Z.; Li, C.; Lin, P.; Rao, M.; Nie, Y.; Song, W.; Qiu, Q.; Li, Y.; Yan, P.; Strachan, J.P.; et al. In situ training of feed-forward and recurrent convolutional memristor networks. Nat. Mach. Intell. 2019, 1, 434–442.

- Yao, P.; Wu, H.; Gao, B.; Tang, J.; Zhang, Q.; Zhang, W.; Yang, J.J.; Qian, H. Fully hardware-implemented memristor convolutional neural network. Nature 2020, 577, 641–646.

- Yao, P.; Wu, H.; Gao, B.; Eryilmaz, S.B.; Huang, X.; Zhang, W.; Zhang, Q.; Deng, N.; Shi, L.; Wong, H.S.P.; et al. Face classification using electronic synapses. Nat. Commun. 2017, 8, 5199.

- Liu, X.; Huang, Y.; Zeng, Z.; Wunsch, D.C. Memristor-based HTM spatial pooler with on-device learning for pattern recognition. IEEE Trans. Syst. Man Cybern. Syst. 2020, 3, 5612.

- Krestinskaya, O.; James, A.P. Approximate probabilistic neural networks with gated threshold logic. In Proceedings of the 2018 IEEE 18th International Conference on Nanotechnology, Cork, Ireland, 23–26 July 2018; Volume 18, p. 6302.

- Yu, Y.; Adu, K.; Tashi, N.; Anokye, P.; Wang, X.; Ayidzoe, M.A. RMAF: Relu-Memristor-Like Activation Function for Deep Learning. IEEE Access 2020, 8, 72727–72741.

- Alibart, F.; Zamanidoost, E.; Strukov, D.B. Pattern classification by memristive crossbar circuits using ex situ and in situ training. Nat. Commun. 2013, 4, 3072.

- Bayat, F.M.; Prezioso, M.; Chakrabarti, B.; Nili, H.; Kataeva, I.; Strukov, D. Implementation of multilayer perceptron network with highly uniform passive memristive crossbar circuits. Nat. Commun. 2018, 9, 4482.

- Lin, P.; Li, C.; Wang, Z.; Li, Y.; Jiang, H.; Song, W.; Rao, M.; Zhuo, Y.; Upadhyay, N.K.; Barnell, M.; et al. Three-dimensional memristor circuits as complex neural networks. Nat. Electron. 2020, 3, 225–232.

- Zhang, W.; Gao, B.; Yao, P.; Tang, J.; Qian, H.; Wu, H. Array-level boosting method with spatial extended allocation to improve the accuracy of memristor based computing-in-memory chips. Sci. China Inf. Sci. 2021, 64, 3198.

- Chu, M.; Kim, B.; Park, S.; Hwang, H.; Jeon, M.; Lee, B.H.; Lee, B.G. Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. IEEE Trans. Ind. Electron. 2015, 62, 2410–2419.

- Chiu, P.F.; Nikolić, B. A differential 2R crosspoint RRAM array with zero standby current. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 461–465.

- Wen, S.; Wei, H.; Zeng, Z.; Huang, T. Memristive fully convolutional network: An accurate hardware image-segmentor in deep learning. IEEE Trans. Emerg. Top. Comput. Intell. 2018, 2, 324–334.

- Xiu, C.; Li, X. Edge extraction based on memristor cell neural network with fractional order template. IEEE Access 2019, 7, 90750–90759.

- Wu, Q.; Dang, B.; Lu, C.; Xu, G.; Yang, G.; Wang, J.; Chuai, X.; Lu, N.; Geng, D.; Wang, H.; et al. Spike encoding with optic sensory neurons enable a pulse coupled neural network for ultraviolet image segmentation. Nano Lett. 2020, 20, 8015–8023.

- Chen, J.; Wu, Y.; Yang, Y.; Wen, S.; Shi, K.; Bermak, A.; Huang, T. An efficient memristor-based circuit implementation of squeeze-and-excitation fully convolutional neural networks. IEEE Trans. Neural Netw. Learn. Syst. 2021, 4, 4047.

- Tsai, H.; Ambrogio, S.; MacKin, C.; Narayanan, P.; Shelby, R.M.; Rocki, K.; Chen, A.; Burr, G.W. Inference of long-short term memory networks at software-equivalent accuracy using 2.5M analog phase change memory devices. Dig. Tech. Pap.—Symp. VLSI Technol. 2019, 2019, T82–T83.

- Li, C.; Wang, Z.; Rao, M.; Belkin, D.; Song, W.; Jiang, H.; Yan, P.; Li, Y.; Lin, P.; Hu, M.; et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 2019, 1, 49–57.

- Farkhani, H.; Tohidi, M.; Farkhani, S.; Madsen, J.K.; Moradi, F. A low-power high-speed spintronics-based neuromorphic computing system using real-time tracking method. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 627–638.

- Hu, W.; Luo, H.; Chen, C.; Wei, R. A multi-interval homotopy analysis method using multi-objective optimization for analytically analyzing chaotic dynamics in memristive circuit. IEEE Access 2019, 7, 116328–116341.

More