# Modeling/Performance Analysis of Nanocarbon Interconnects

Subjects: Nanoscience & Nanotechnology Contributor: Wen-Sheng Zhao

As the interconnect delay exceeds the gate delay, the integrated circuit (IC) technology has evolved from a transistorcentric era to an interconnect-centric era. Conventional metallic interconnects face several serious challenges in aspects of performance and reliability. To address these issues, nanocarbon materials, including carbon nanotube (CNT) and graphene, have been proposed as promising candidates for interconnect applications.

Keywords: nano-interconnect ; carbon nanotube ; graphene

# 1. Introduction

The breakthrough development of the semiconductor industry has revolutionized human society, from personal electronic gadgets, commercial and industrial equipment to military and aeronautical facilities. As predicted by Moore's law, the number of transistors within a chip doubles about every two years, while the cost comes down <sup>[1]</sup>. According to the International Technology Roadmap for Semiconductors (ITRS) projection, a 10 nm minimum feature size could support a tera-scale chip with a trillion transistors by 2020 <sup>[2]</sup>. Such phenomenal progress has been achieved through scaling of digital integrated circuit (IC) feature size to smaller physical dimensions.

The ongoing miniaturization of the IC feature size has had a significant benefit in increasing the transistor speed. However, different from the transistor, the interconnect performance would be degraded due to the reduced conduction area and increased scattering probability for electrons <sup>[3][4]</sup>. Under such circumstances, the chip performance is restricted by the shrinking interconnect dimensions on account of both the interconnect delay and the power dissipation. Moreover, the interconnect reliability has been becoming a more and more important problem, as the ampacity of conventional Cu wire cannot satisfy the increasingly stringent requirements <sup>[2][5][6]</sup>. Therefore, interconnects have become the major challenge in the design of modern ICs, thereby leading to the transition of IC technology from transistor-centric to interconnect optimization and design methods have been reported, such as a low-k dielectric structure, three-dimensional integration, and inter-chip optical interconnects <sup>[8][9][10]</sup>.

Nanocarbon materials have attracted much attention since the carbon nanotube (CNT) was discovered by an arcdischarge evaporation method in 1991 <sup>[11]</sup>. Graphene, a Nobel Prize honored discovery, has further promoted the research in this field <sup>[12]</sup>. It was found that nanocarbon materials have many extraordinary physical properties. For example, the ultrahigh thermal conductivity of nanocarbon materials can help heat dissipation in high-density integrated systems <sup>[13][14][15]</sup>. The maximum current-carrying density of a CNT is more than two orders higher than that of Cu wires, thereby mitigating the electromigration-induced reliability problems <sup>[16]</sup>. It is natural to apply nanocarbon materials as an alternative option to potentially replace Cu for interconnects and passive devices in ICs <sup>[17][18][19][20][21][22]</sup>. In recent years, there have been many publications in the literature devoted to the design, modeling/analysis, and fabrication/integration of nanocarbon interconnects.

# 2. Graphene Nanoribbon (GNR) Interconnects

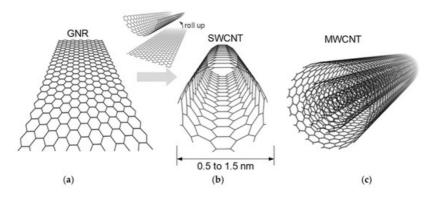

Physically, graphene is a 2D monolayer of carbon atoms packed into a honeycomb lattice, and the quasi-1D graphene nanoribbon (GNR), as shown in <u>Figure 1</u>a, can be utilized as on-chip interconnects <sup>[23]</sup>. Depending on the edge shape, a GNR can be zigzag, armchair, or chiral (other shapes). The zigzag GNR is always metallic, whereas the armchair GNR is metallic or semiconducting, depending on the number of carbon atoms across its width. Different from the GNR, a CNT's chirality is defined by its circumferential edge shape. A single-walled carbon nanotube (SWCNT) can be visualized as a

seamlessly rolled-up GNR, on the basis of which a novel fabrication method has been developed to unzip the CNT to form a GNR <sup>[24]</sup>. A multi-walled carbon nanotube (MWCNT) is a parallel assembly of coaxial SWCNTs, and the neighboring shells in an MWCNT are separated by the van der Waals gap.

**Figure 1.** Schematics of (**a**) monolayer graphene nanoribbon (GNR), (**b**) single-walled carbon nanotube (SWCNT), and (**c**) multi-walled carbon nanotube (MWCNT).

## 3. CNT Interconnects

Similar with GNR, CNT possesses long MFP, high ampacity, and large thermal conductivity  $^{[14][16][25][26][27]}$ . Based on the Luttinger liquid theory, Burke firstly developed the transmission line model of a metallic SWCNT interconnect  $^{[28]}$ . with the CNT diameter denoted as  $D_{cnt}$ . The number of conducting channels of a metallic SWCNT is 2, and the MFP is usually  $1000D_{cnt}$ . Although an SWCNT possesses many unit properties and some efforts have been devoted to reducing the SWCNT resistance by doping, an isolated SWCNT is still too resistive for interconnect applications in high-performance ICs  $^{[29][30]}$ . It can only be used in some specific applications such as subthreshold circuits and sub-10 nm circuits  $^{[31][32][33]}$ . To reduce the CNT resistance, three kinds of CNT interconnects, i.e., monolayer SWCNT, bundled SWCNT, and MWCNT interconnects, have been widely studied, as shown in Figure 2.

Figure 2. Cross-sectional views of (a) monolayer SWCNT, (b) bundled SWCNT, and (c) MWCNT interconnects.

## 4. All-Carbon 3-D Interconnects

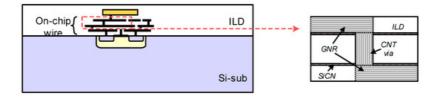

In general, CNTs grow vertically, whereas graphene is formed horizontally. So, it is natural to develop the 3-D interconnects by combining vertical CNT vias and horizontal GNR interconnects, as shown in Figure 3. Nihei, et al. <sup>[34]</sup> firstly conceived, designed and realized the experiment to grow an MWCNT via on multilayer graphene. The critical issue to fabricate such "all-carbon" 3-D interconnects is to achieve a low electrical contact between the CNT via and the GNR interconnect. Further, Ramos, et al. <sup>[35]</sup> introduced a process to selectively grow CNTs on monolayer graphene. They demonstrated that the growth of CNTs would not damage the integrity of graphene and characterized the contact resistance between CNTs and graphene. Zhou, et al. <sup>[36]</sup> studied the CNT-graphene interface using transmission electron microscope and found that C-C bonding exists between CNT and graphene. Recently, Jiang, et al. <sup>[37]</sup> comprehensively investigated the fabrication, integration, and reliability of such "all-carbon" 3-D interconnects. Besides, it is worth noting that another "all-carbon" 3-D interconnect scheme, i.e., a dense vertical and horizontal graphene structure, has been demonstrated in <sup>[34]</sup>.

Figure 3. Schematic of all-carbon 3-D interconnect.

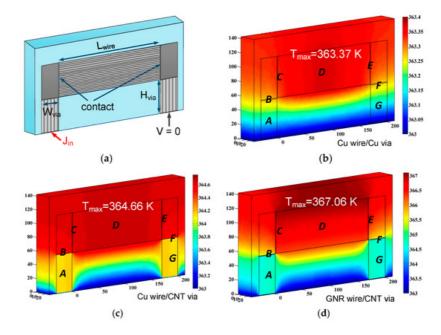

Using the finite-element method (FEM), the electrothermal characteristics of all-carbon 3-D interconnects have been studied in <sup>[38]</sup>. <u>Figure 4</u>a shows the simulation model, which is formed by one horizontal interconnect and two vertical vias. The 3-D interconnect structure is embedded into an interlayer dielectric, whose thermal conductivity is about 0.12 W/m·K. The bottom temperature is assumed as 363 K, and the other boundaries are set as adiabatic. The out-plane electrical conductivity of the MLGNR is 1 S/m. The geometrical parameters are adopted at the 22 nm technology node from the ITRS projection <sup>[2]</sup>. With a current of 0.4 mA injected, the temperature profiles are plotted in <u>Figure 4</u>b–d. In the simulation,

a 1 nm-thick thin plate was used to capture the influences of contact resistance. Due to the impact of quantum contact resistance, all-carbon 3-D interconnect is more resistive than Cu counterpart, thereby increasing the temperature rise. On the contrary, the CNT vias help heat dissipation from hotspots to the bottom layer. Therefore, the maximum temperature is slightly increased with the implementation of all-carbon 3-D interconnects. The results also imply that CNT vias are more suitable to be placed near bottom layer.

**Figure 4.** (a) Schematic of a simulation model. (b–d) Temperature profiles of Cu, SWCNT vias/Cu wire, and SWCNT/MLG interconnects <sup>[38]</sup>.

## 5. Cu-Nanocarbon Interconnect

#### 5.1. Cu-Graphene Interconnect

During the past decades, tremendous progress has been made in the fabrication/integration of nanocarbon interconnects. However, the gap between theoretical studies and practical applications still exists. For example, the assumption of closed packed CNTs is invalid as the density of CNTs still cannot satisfy the requirements <sup>[39]</sup>. Also, the application of MLGNR interconnects encounters a serious challenge, i.e., graphene tends to behave more like graphite as the number of graphene layers increases <sup>[40]</sup>. In this perspective, Cu/low-k interconnect may be still a good choice for next-generation ICs <sup>[41]</sup>.

In the application of Cu/low-k interconnect, a highly resistive diffusion barrier layer is required to prevent the diffusion of copper atoms into substrate. This barrier layer would occupy a certain area, thereby decreasing the conduction area of interconnects and increasing the effective resistivity. More importantly, the barrier layer thickness cannot scale as rapidly as the interconnect dimensions <sup>[4]</sup>. This problem becomes more and more serious with the technology advanced. To resolve this problem, graphene, the thinnest 2-D material in nature, has been proposed as the ultimate barrier layer <sup>[42][43]</sup> <sup>[44]</sup>. It has been demonstrated that graphene barrier layer can help improving the breakdown current density, enhancing the electromigration lifetime, increasing the Cu grain size, and reducing the scattering probability at the surface <sup>[45][46][47]</sup> <sup>[48][49]</sup>. Moreover, low-temperature deposition techniques for producing graphene on Cu and dielectric implies that the fabrication of graphene barrier layer can be compatible with traditional CMOS technology <sup>[44][47][50][51]</sup>.

#### 5.2. Cu-CNT Composite Interconnect

Generally speaking, nanocarbon and conventional metals have their own pros and cons for interconnect applications. For instance, nanocarbon has high ampacity, but their conductivity is still low due to fabrication limits. On the contrary, the fabrication and integration processes of metal interconnects are mature, but the ampacity of metals cannot satisfy the requirements <sup>[2]</sup>. Subramaniam, et al. <sup>[52]</sup> attempted to advance a possible solution to this problem by co-depositing Cu with CNTs, i.e., Cu-CNT composite interconnect. It was experimentally demonstrated that Cu-CNT composite interconnect can achieve a balance between performance and reliability. This is, such Cu-CNT composite interconnect possesses a 100 times higher ampacity, but comparable conductivity than the Cu counterpart. The presence of CNTs inside Cu wire can also alleviate the electromigration void growth rate by about four times, which is due to large Lorenz number of the CNTs <sup>[53][54]</sup>.

## 6. Conclusions

The current status of research on nanocarbon interconnects from a modeling perspective has been reviewed in this work. Several typical nanocarbon interconnects have been evaluated and discussed. It is demonstrated that nanocarbon interconnects are theoretically superior to their Cu counterparts. However, due to the fabrication limits, the electrical performance of nanocarbon interconnects may be much worse than their theoretical estimations. Cu-nanocarbon interconnects, including Cu-graphene and Cu-CNT composite interconnects, may be a practical solution to meet the near future challenges. With the IC feature size scaling down to sub-10 nm, however, nanocarbon interconnects are the most promising schemes. This is to say, in long-term applications, Cu-nanocarbon interconnects may be used together with the ultimate nanocarbon interconnects.

#### References

- 1. Moore, G.E. Cramming more components onto integrated circuits. Electronics 1965, 38, 114-117.

- International Technology Roadmap for Semiconductors, Edition 2013. Available online: http://www.itrs2.net/ (accessed on 1 August 2017).

- 3. Davis, J.A.; Venkatesan, R.; Kaloyeros, A.; Beylansky, M.; Souri, S.J.; Banerjee, K.; Saraswat, K.C.; Rahman, A.; Reif, R.; Meindl, J.D. Interconnect limits on gigascale integration (GSI) in the 21st century. Proc. IEEE 2001, 89, 305–324.

- Banerjee, K.; Souri, S.J.; Kapur, P.; Saraswat, K.C. 3-D ICs: A novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration. Proc. IEEE 2001, 89, 602–633.

- 5. Li, B.; Sullivan, T.D.; Lee, T.C.; Badami, D. Reliability challenges for copper interconnects. Microelectron. Reliab. 2004, 44, 365–380.

- Zhang, R.; Yang, K.; Metaev, E.; Pesic, M.; Lloyd, J.; Ring, M.; Paliwoda, P.; Tan, S.; Young, C.; Verzellsi, G.; et al. Reliability and modeling: What to simulate and how? In Proceedings of the INVITED IEEE International Integrated Reliability Workshop (IEEE IIRW), Fallen Leaf Lake, CA, USA, 8–12 October 2017.

- 7. Meindl, J.D. Beyond Moore's law: The interconnect era. Comput. Sci. Eng. 2003, 5, 20–24.

- Ryan, J.G.; Geffken, R.M.; Poulin, N.R.; Paraszcazak, J.R. The evolution of interconnection technology at IBM. IBM J. Res. Dev. 1995, 39, 371–381.

- Hayakawa, H.; Yoshikawa, N.; Yorozu, S.; Fujimaki, A. Superconducting digital electronics. Proc. IEEE 2004, 92, 1549– 1563.

- 10. Sun, C.; Wade, M.T.; Lee, Y.; Orcutt, J.S.; Alloatti, L.; Georgas, M.S.; Waterman, A.S.; Shainline, J.M.; Avizienis, R.R.; Lin, S.; et al. Single-chip microprocessor than communicates directly using light. Nature 2015, 528, 534–538.

- 11. lijima, S. Helical microtubules of graphitic carbon. Nature 1991, 354, 56-58.

- 12. Novoselov, K.S.; Geim, A.K.; Morozov, S.V.; Jiang, D.; Zhang, Y.; Dubonos, S.V.; Grigorieva, I.V.; Firsov, A.A. Electric field effect in atomically thin carbon films. Science 2004, 306, 666–669.

- 13. Balandin, A.A.; Ghosh, S.; Bao, W.; Calizo, I.; Teweldebrhan, D.; Miao, F.; Lau, C.N. Superior thermal conductivity of single-layer graphene. Nano Lett. 2008, 8, 902–907.

- 14. Berber, S.; Kwon, Y.K.; Tomanek, D. Unusually high thermal conductivity of carbon nanotubes. Phys. Rev. Lett. 2000, 84, 4613.

- 15. Prasher, R. Graphene spreads the heat. Science 2010, 328, 185–186.

- Wei, B.Q.; Vajtai, R.; Ajayan, P.M. Reliability and current carrying capacity of carbon nanotubes. Appl. Phys. Lett. 2001, 79, 1172–1174.

- 17. Pop, E.; Mann, D.; Reifenberg, J.; Goodson, K.; Dai, H. Electro-thermal transport in metallic single-wall carbon nanotubes for interconnect applications. IEDM Tech. Dig. 2005, 253-256.

- Li, H.; Xu, C.; Srivastava, N.; Banerjee, K. Carbon nanomaterials for next-generation interconnects and passives: Physics, status, and prospects. IEEE Trans. Electron Devices 2009, 56, 1799–1821.

- 19. Maffucci, A. Carbon nanotubes in nanopackaging applications. IEEE Nanotechnol. Mag. 2009, 3, 22–25.

- Chiariello, A.G.; Maffucci, A.; Miano, G. Circuit models of carbon-based interconnects for nanopackaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1926–1937.

- 21. Maffucci, A.; Miano, G. Electrical properties of graphene for interconnect applications. Appl. Sci. 2014, 4, 305–317.

- 22. Zhao, W.S.; Yin, W.Y. Carbon-based interconnects for RF nanoelectronics. Wiley Encycl. Electr. Electron. Eng. 2012, 1–20, doi: 10.1002/047134608X.W8147.

- 23. Behnam, A.; Lyons, A.S.; Bae, M.H.; Chow, E.K.; Islam, S.; Neumann, C.M.; Pop, E. Transport in nanoribbon interconnects obtained from graphene grown by chemical vapor deposition. Nano Lett. 2012, 12, 4424–4430.

- 24. Kosynkin, D.V.; Higginbotham, A.L.; Sinitskii, A.; Lomeda, J.R.; Dimiev, A.; Price, B.K.; Tour, J.M. Longitudinal unzipping of carbon nanotubes to form graphene nanoribbon. Nature 2009, 458, 872–876.

- 25. Li, F.; Cheng, H.M.; Bai, S.; Su, G.; Dresselhaus, M.S. Tensile strength of single-walled carbon nanotubes directly measured from their macroscopic ropes. Appl. Phys. Lett. 2000, 77, 3161–3163.

- 26. Li, H.J.; Lu, W.G.; Li, J.J.; Bai, X.D.; Gu, C.Z. Multichannel ballistic transport in multiwall carbon nanotubes. Phys. Rev. Lett. 2005, 95, 86601.

- 27. Maffucci, A.; Micciulla, F.; Cataldo, A.E.; Miano, G.; Bellucci, S. Modeling, fabrication, and characterization of large carbon nanotube interconnects with negative temperature coefficient of the resistance. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 485–493.

- 28. Burke, P.J. Luttinger liquid theory as a model of the gigahertz electrical properties of carbon nanotubes. IEEE Trans. Nanotechnol. 2002, 99, 129–144.

- 29. Liang, J.; Lee, J.; Berrada, S.; Georgiev, V.P.; Pandey, R.; Chen, R.; Asenov, A.; Todri-Sanial, A. Atomistic- to circuitlevel modeling of doped SWCNT for on-chip interconnects. IEEE Trans. Nanotechnol. 2018, 17, 1084–1088.

- Miano, G.; Forestiere, C.; Maffucci, A.; Maksimenko, S.A.; Slepyan, G.Y. Signal propagation in carbon nanotubes of arbitrary chirality. IEEE Trans. Nanotechnol. 2011, 10, 135–149.

- Jamal, O.; Naeemi, A. Ultralow-power single-wall carbon nanotube interconnects for subthreshold circuits. IEEE Trans. Nanotechnol. 2011, 10, 99–101.

- 32. Pable, S.D.; Hasan, M. Interconnect design for subthreshold circuits. IEEE Trans. Nanotechnol. 2012, 11, 633-639.

- Ceyhan, A.; Naeemi, A. Cu interconnect limitations and opportunities for SWNT interconnects at the end of the roadmap. IEEE Trans. Electron Devices 2013, 60, 374–382.

- Nihei, M.; Kawabata, A.; Murakami, T.; Sato, M.; Yokoyama, N. CNT/graphene technologies for future carbon-based interconnects. In Proceedings of the IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, Xi'an, China, 29 October–1 November 2012; pp.1–4.

- 35. Ramos, R.; Fournier, A.; Fayolle, M.; Dijon, J.; Murray, C.P.; McKenna, J. Nanocarbon interconnects combining vertical CNT interconnects and horizontal graphene lines. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 48–50.

- 36. Zhou, C.; Senegor, R.; Baron, Z.; Chen, Y.; Raju, S.; Vyas, A.A.; Chan, M.; Chai, Y.; Yang, C.Y. Synthesis and interface characterization of CNTs on graphene. Nanotechnology 2017, 28, 054007.

- Jiang, J.; Kang, J.; Chu, J.H.; Banerjee, K. All-carbon interconnect scheme integrating graphene-wires and carbonnanotube-vias. IEDM Tech. Dig. 2017, 1431–1434.

- 38. Li, N.; Mao, J.; Zhao, W.S.; Tang, M.; Chen, W.; Yin, W.Y. Electrothermal cosimulation of 3-D carbon-based heterogeneous interconnects. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 518–526.

- 39. Zhang, G.; Warner, J.H.; Fouque, M.; Robertson, A.W.; Chen, B.; Robertson, J. Growth of ultrahigh density singlewalled carbon nanotube forests by improved catalyst design. ACS Nano 2012, 6, 2893–2903.

- 40. Eda, G.; Fanchini, G.; Chhowalla, M. Large-area ultrathin films of reduced graphene oxide as a transparent and flexible electronic material. Nat. Nanotechnol. 2008, 3, 270–274.

- 41. Ceyhan, A.; Naeemi, A. Cu/low-k interconnect technology design and benchmarking for future technology nodes. IEEE Trans. Electron Devices 2013, 60, 4041–4047.

- 42. Nguyen, B.S.; Lin, J.F.; Perng, D.C. 1-nm-thick graphene tri-layer as the ultimate copper diffusion barrier. Appl. Phys. Lett. 2014, 104, 082105.

- 43. Hong, J.; Lee, S.; Lee, S.; Han, H.; Mahata, C.; Yeon, H.W.; Koo, B.; Kim, S.I.; Nam, T.; Byun, K.; et al. Graphene as an atomically thin barrier to Cu diffusion into Si. Nanoscale 2014, 6, 7503–7511.

- 44. Li, L.; Chen, X.; Wang, C.H.; Cao, J.; Lee, S.; Tang, A.; Ahn, C.; Roy, S.S.; Arnold, M.S.; Wong, H.S.P. Vertical and lateral copper transport through graphene layers. ACS Nano 2015, 9, 8361–8367.

- 45. Kang, C.G.; Lim, S.K.; Lee, S.; Lee, S.K.; Cho, C.; Lee, Y.G.; Hwang, H.J.; Kim, Y.; Choi, H.J.; Choe, S.H. Effects of multi-layer graphene capping on Cu interconnects. Nanotechnology 2013, 24, 115707.

- 46. Zhang, R.; Zhao, W.S.; Hu, J.; Yin, W.Y. Electrothermal characterization of multilevel Cu-graphene heterogenesou interconnects in the presence of an electrostatic discharge (ESD). IEEE Trans. Nanotechnol. 2015, 14, 205–209.

- 47. Mehta, R.; Chugh, S.; Chen, Z. Enhanced electrical and thermal conduction in graphene-encapsulated copper nanowires. Nano Lett. 2015, 15, 2024–2030.

- 48. Goli, P.; Ning, H.; Li, X.; Liu, C.Y.; Novoselov, K.S.; Balandin, A.A. Thermal properties of graphene-copper-graphene heterogeneous films. Nano Lett. 2014, 14, 1497–1503.

- 49. Li, L.; Zhu, Z.; Yoon, A.; Wong, H.S.P. In-situ grown graphene enables copper interconnects with improved eletromigration reliability. IEEE Electron Device Lett. 2019, doi:10.1109/LED.2019.2908426.

- 50. Mehta, R.; Chugh, S.; Chen, Z. Transfer-free multi-layer graphene as a diffusion barrier. Nanoscale 2017, 9, 1827–1833.

- 51. Li, C.L.; Zhang, S.; Shen, T.; Appenzeller, J.; Chen, Z. BEOL compatible 2D layered materials as ultra-thin diffusion barriers for Cu interconnect technology. In Proceedings of the IEEE 75th Annual Device Research Conference (DRC), South Bend, IN, USA, 25–28 June 2017; pp. 1–2.

- 52. Subramaniam, C.; Yamada, T.; Kobashi, K.; Sekiguchi, A.; Futaba, D.N.; Yumura, M.; Hata, K. One hundred fold increase in current carrying capacity in a carbon nanotube-copper composite. Nat. Commun. 2013, 4, 2202.

- 53. Chai, Y.; Chan, P.C.H.; Fu, Y.; Chuang, Y.C.; Liu, C.Y. Electromigraiton studies of Cu/carbon nanotube composite interconnects using Blech structure. IEEE Electron Device Lett. 2008, 29, 1001–1003.

- 54. Lee, J.; Berrada, S.; Adamu-Lema, F.; Nagy, N.; Georgiev, V.P.; Sadi, T.; Liang, J.; Ramos, R.; Carrillo-Nunez, H.; Kalita, D.; et al. Understanding electromigration in Cu-CNT composite interconnects: A multiscale electrothermal simulation study. IEEE Trans. Electron Devices 2018, 65, 3884–3892.

Retrieved from https://encyclopedia.pub/entry/history/show/6504